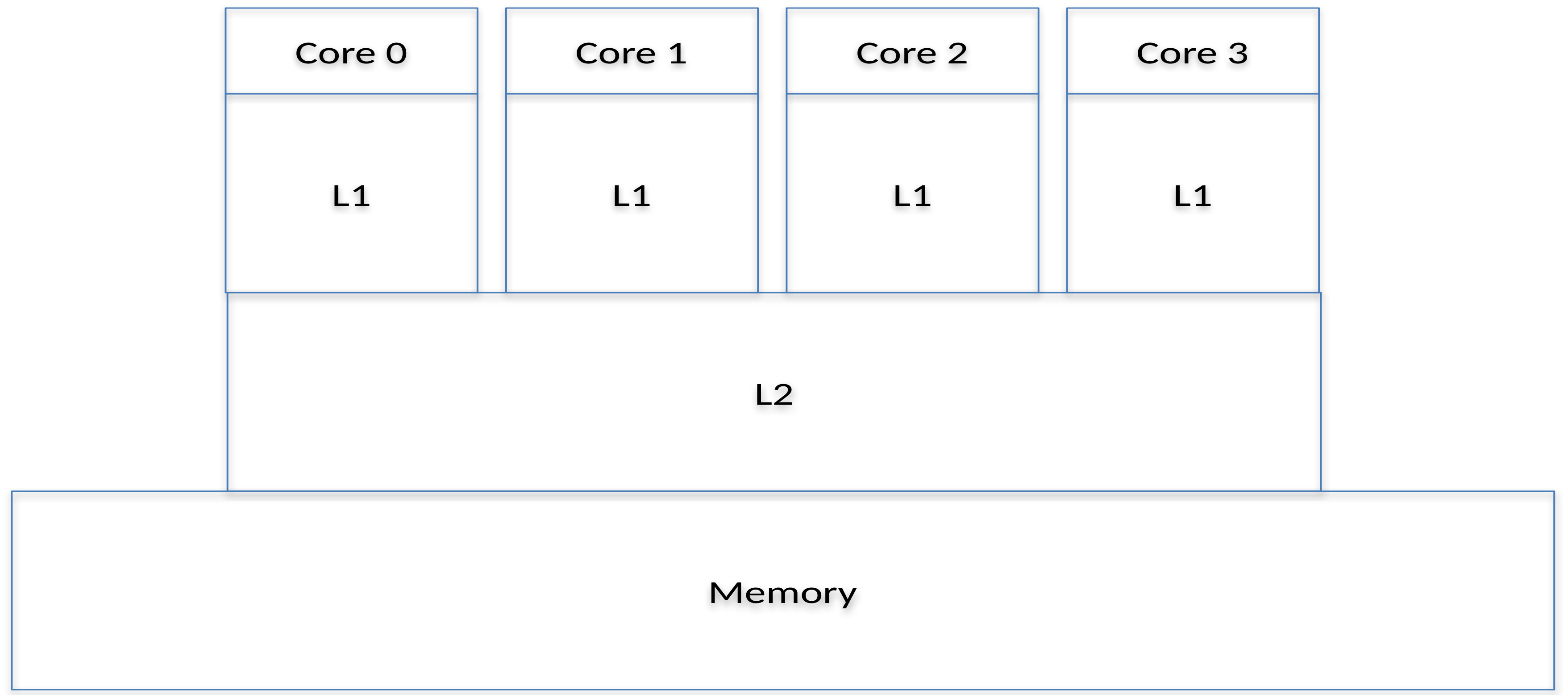

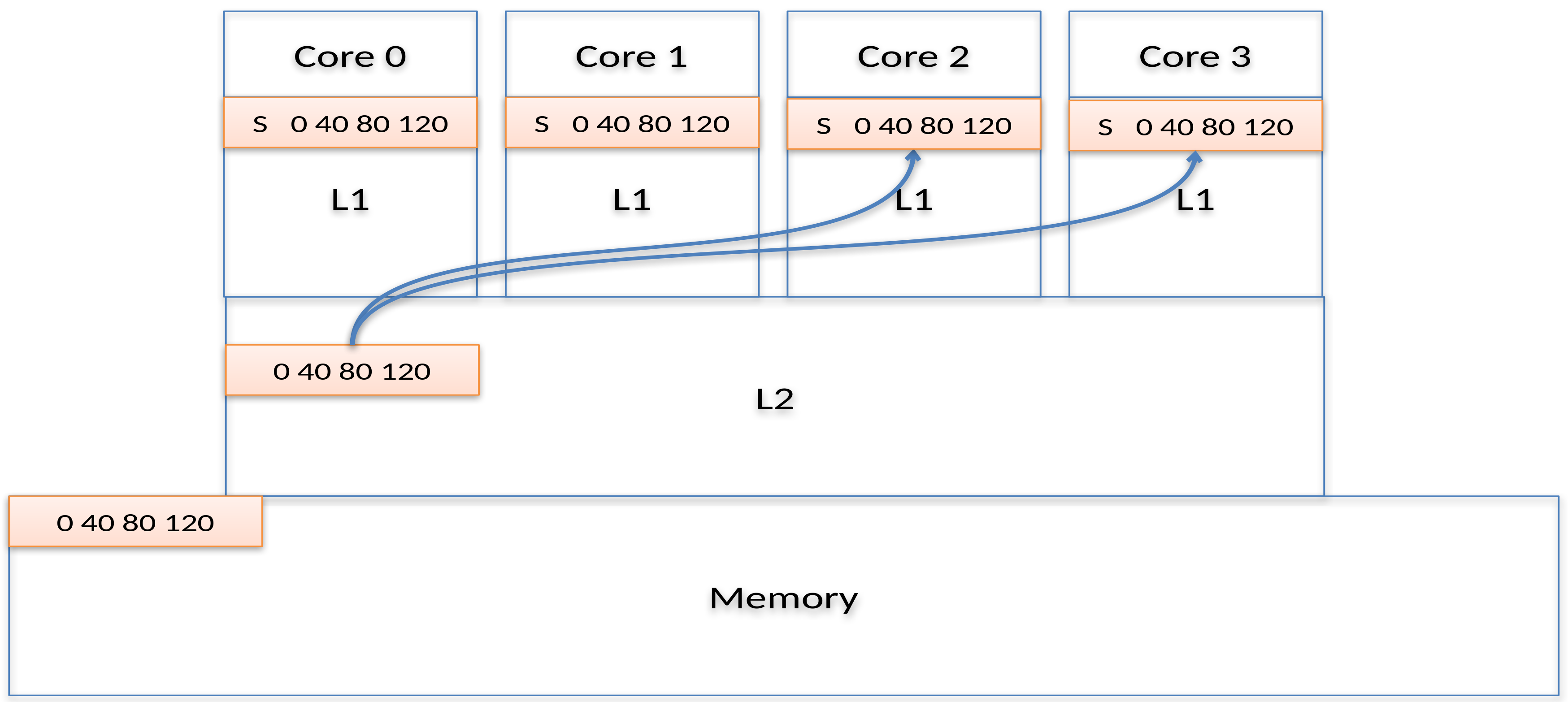

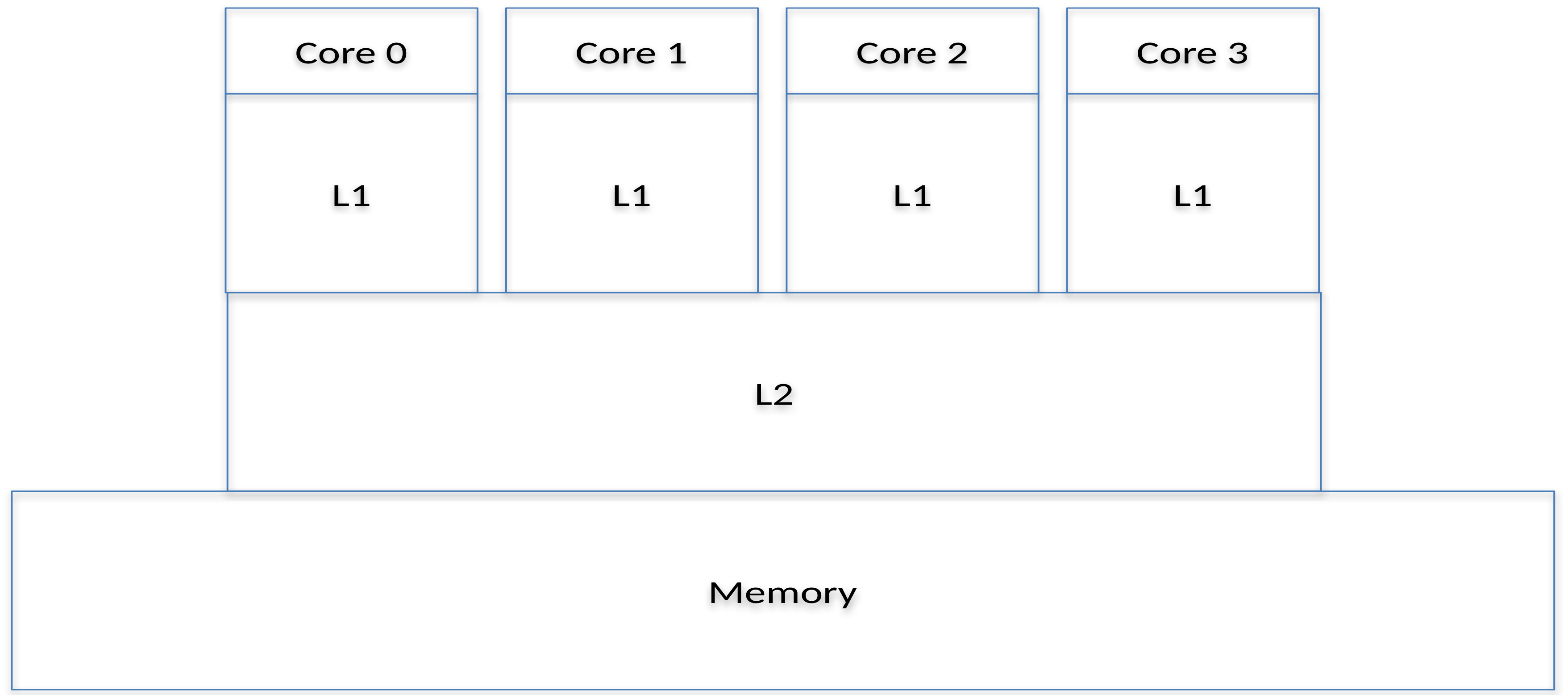

Diagrama do sistema

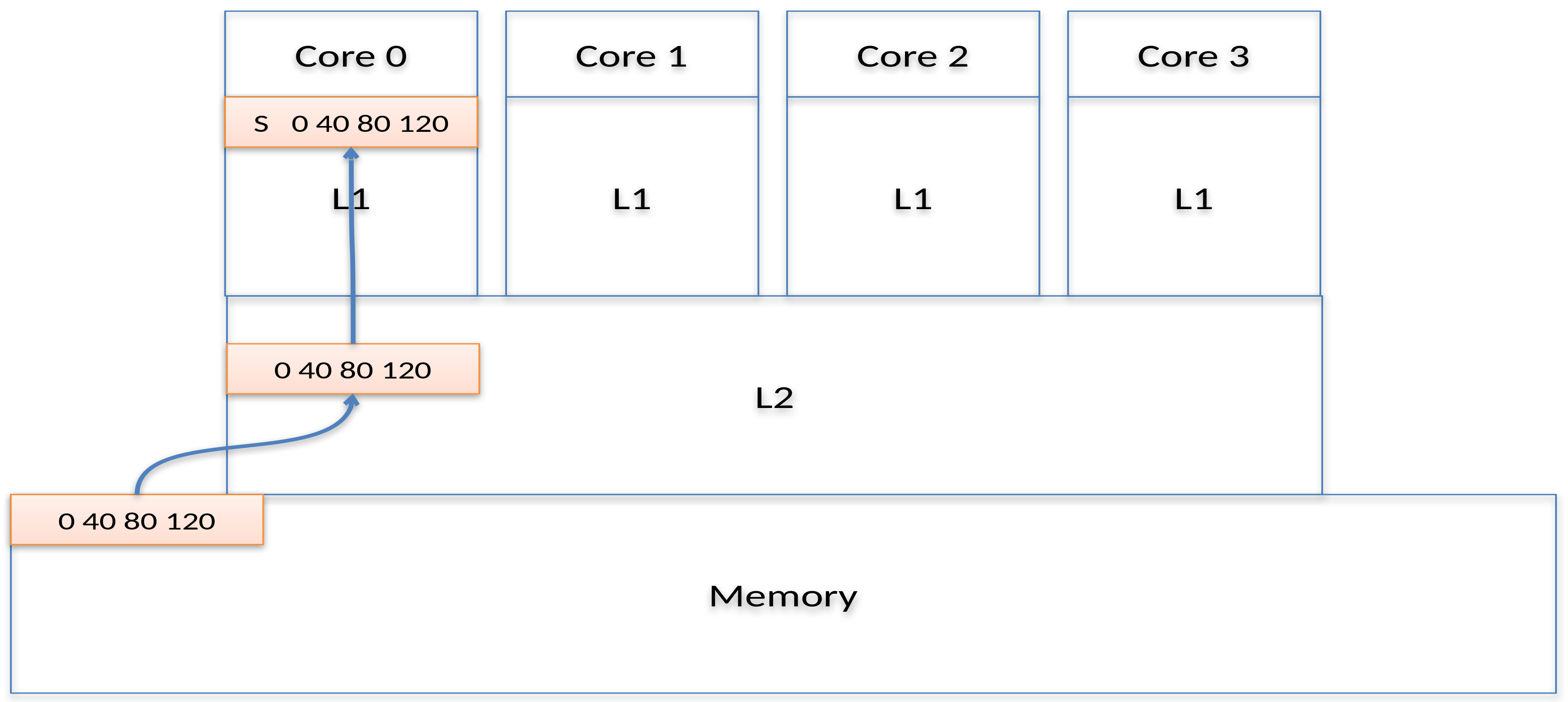

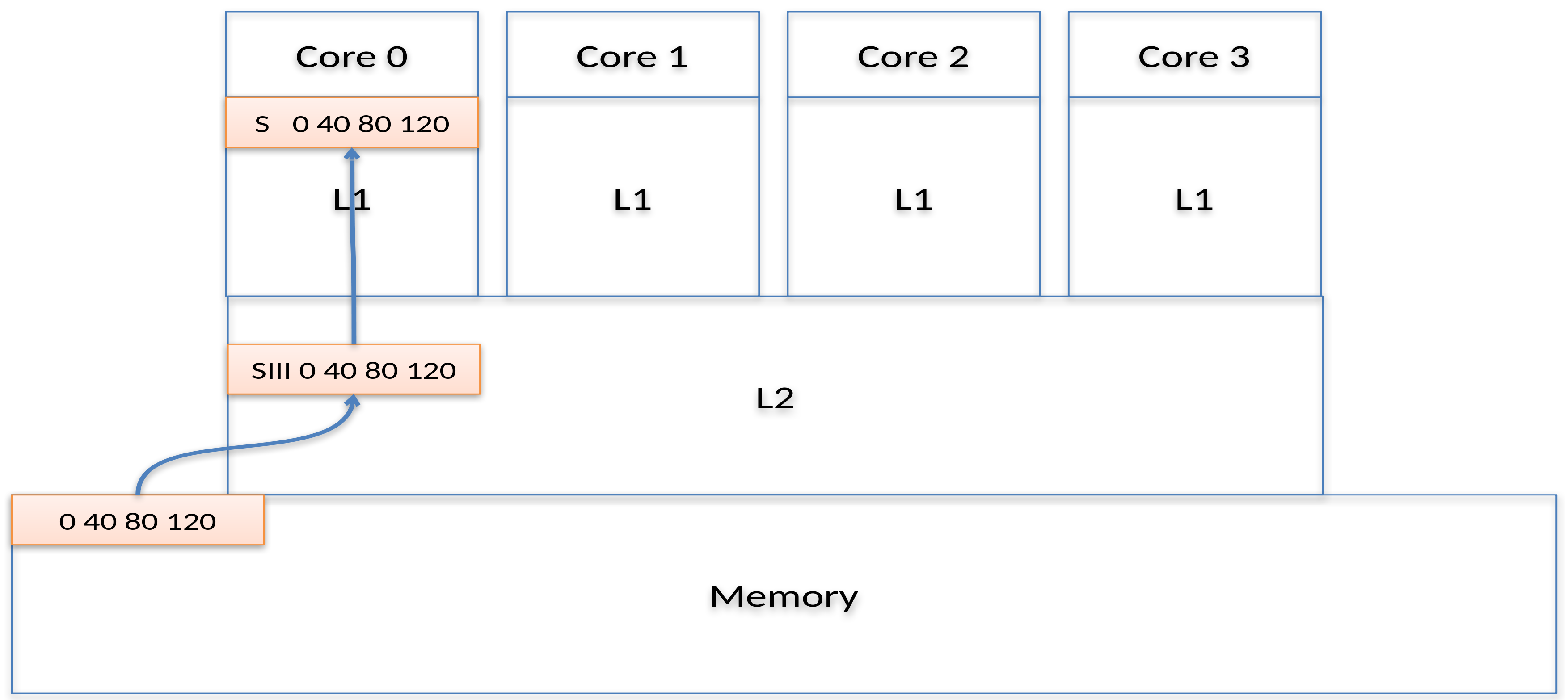

C0: READ(0);

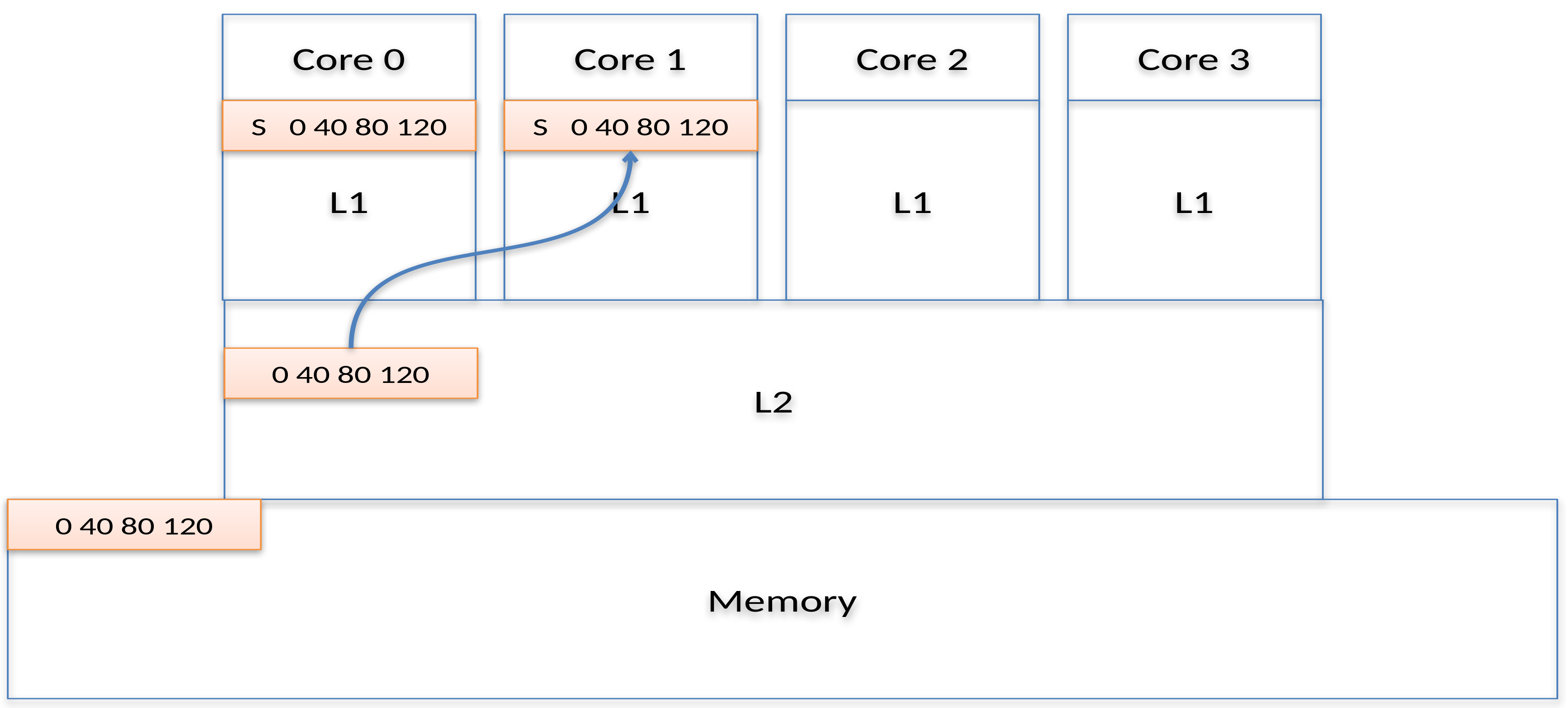

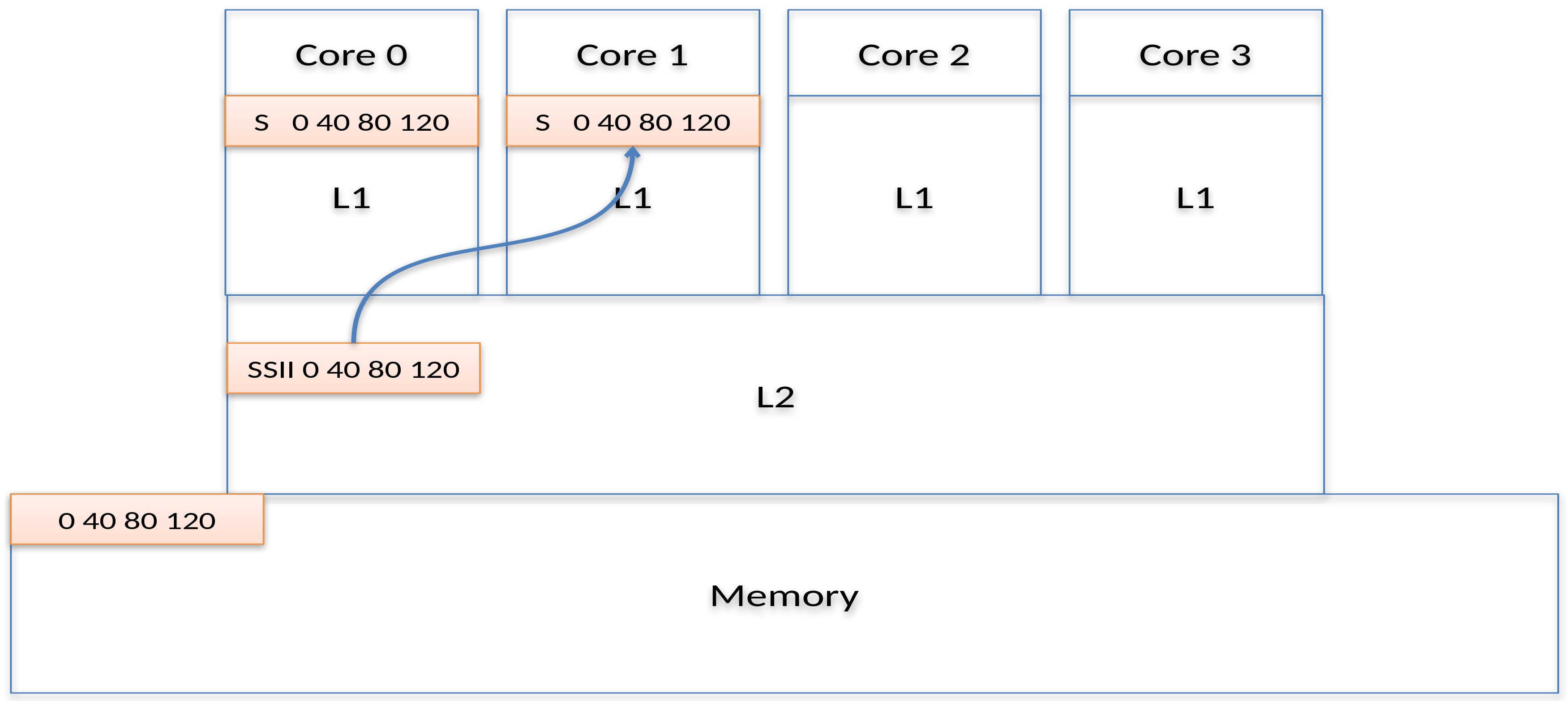

C0: READ(0); C1: READ(0);

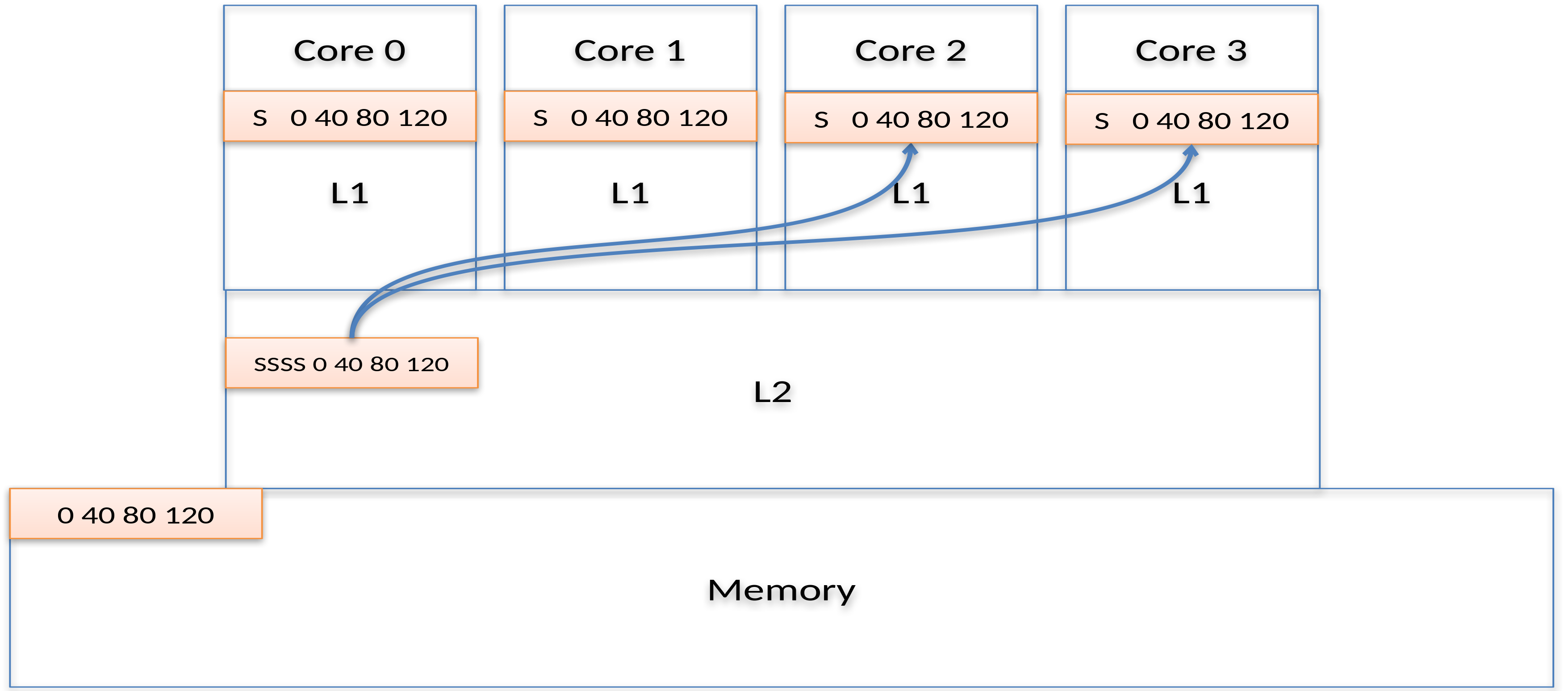

C0: READ(0); C1: READ(0); C2: READ(0); C3: READ(0);

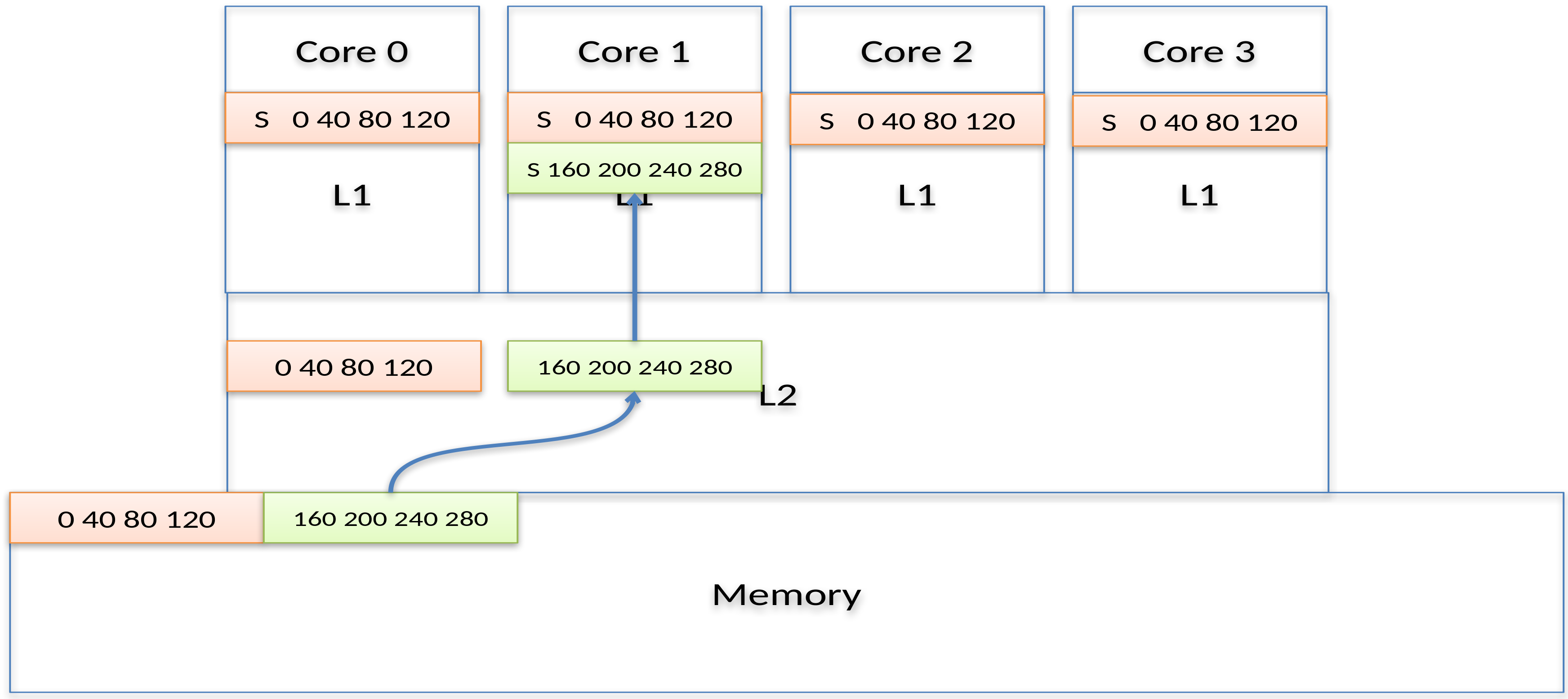

C1: READ(16);

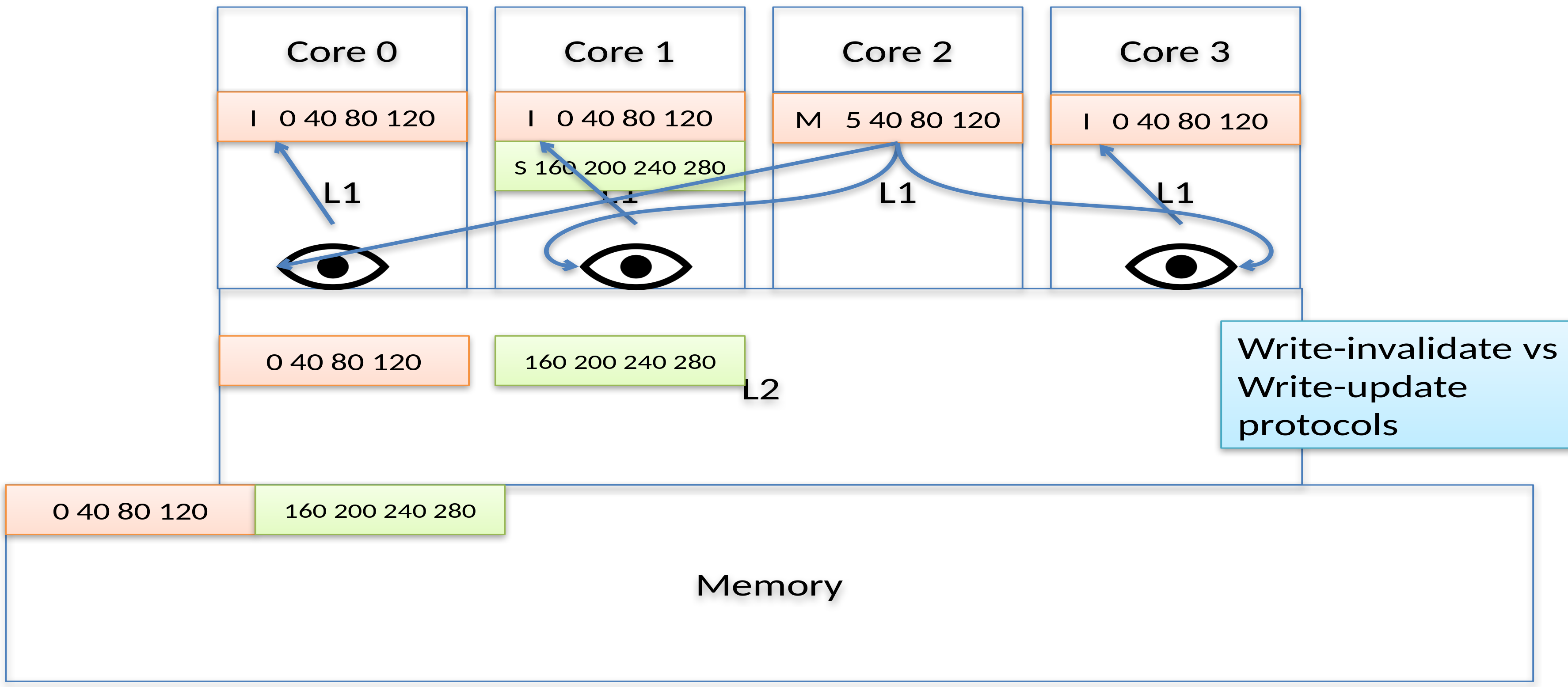

C1: READ(16); C2: WRITE(0, 5);

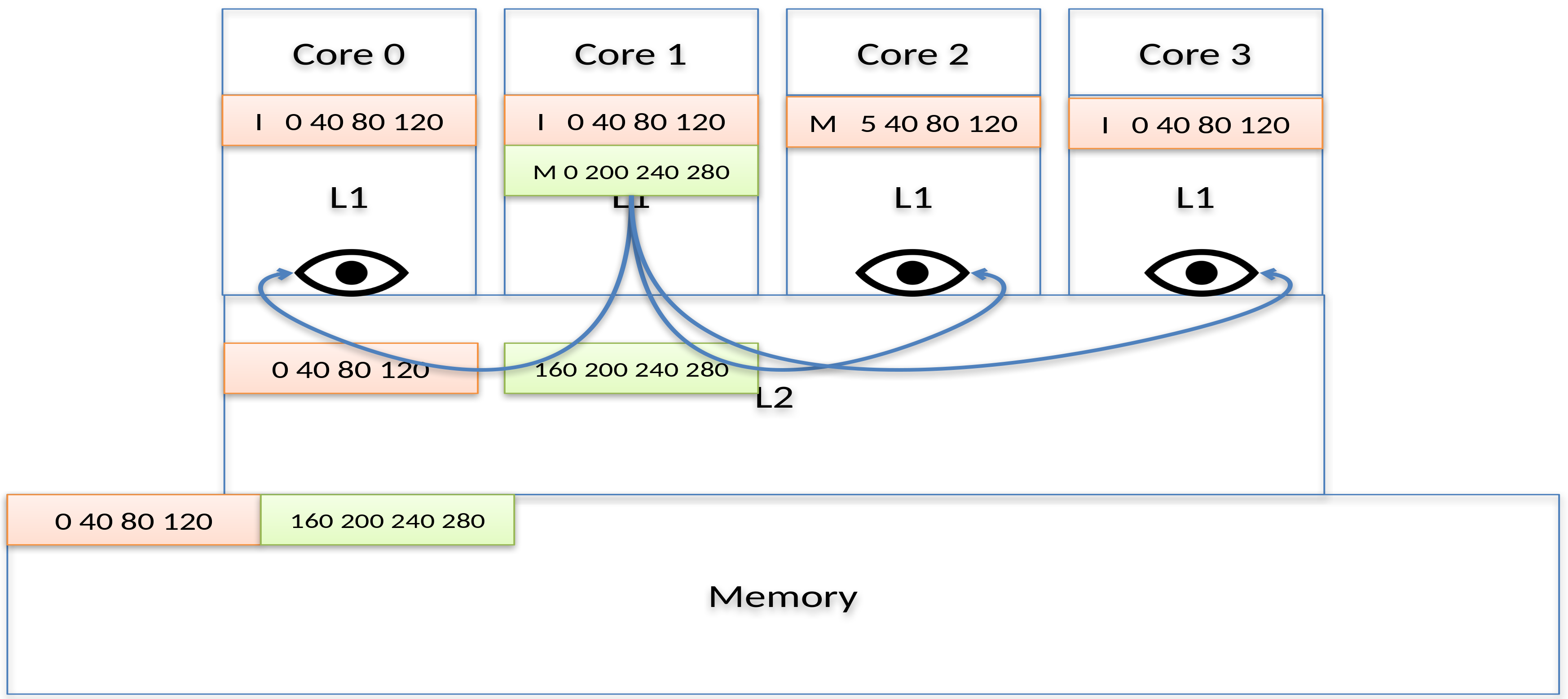

C1: READ(16); C2: WRITE(0, 5); C1: WRITE(16, 0)

C1: READ(16); C2: WRITE(0, 5); C1: WRITE(16, 0); C3: READ(16);

C0: WRITE(8, 0);

C0: WRITE(8, 0);

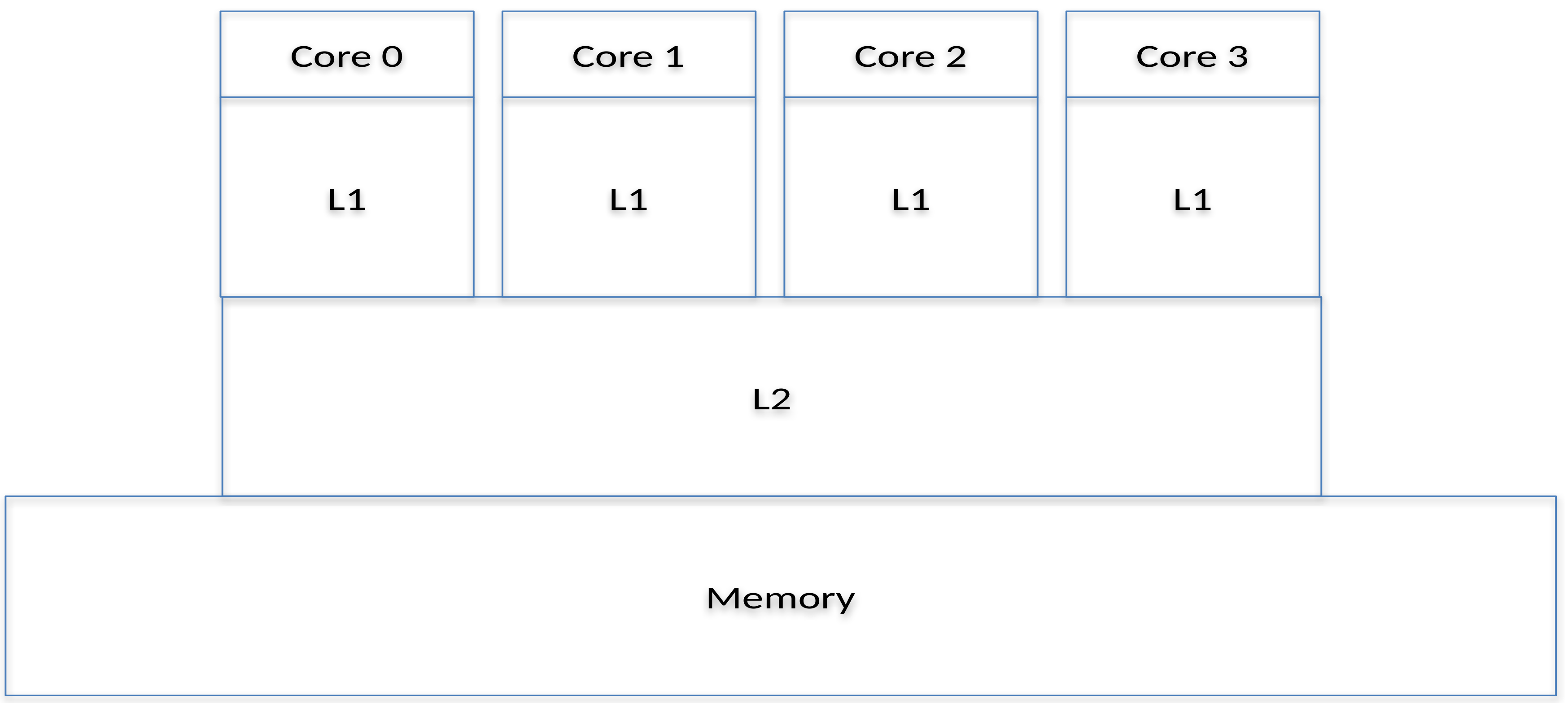

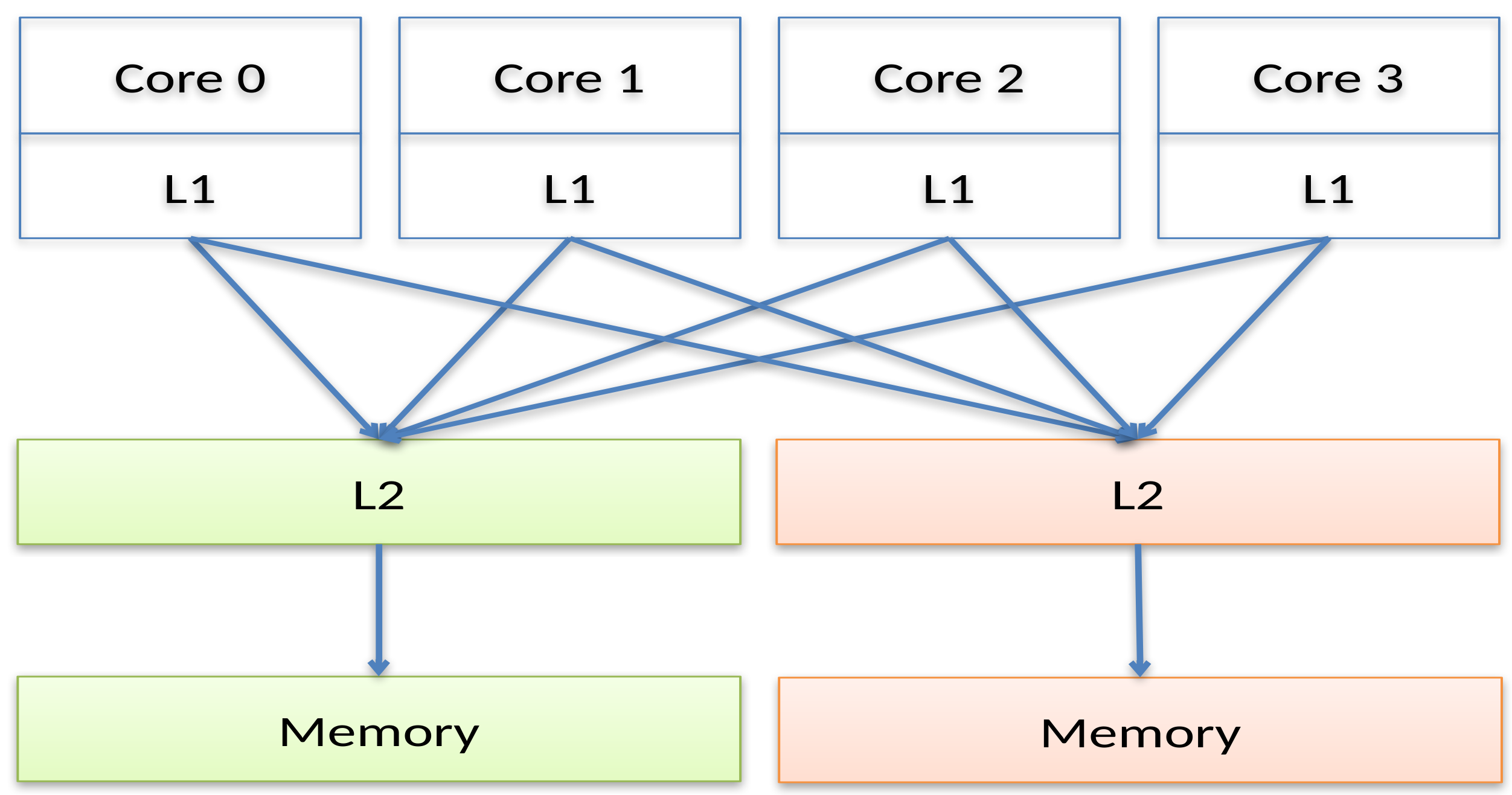

Diretório

- Ponto centralizado para todas as informações de coerência

- Normalmente é armazenado dentro da cache de último nível (LLC) quando ela é inclusiva

- Para caches particionadas (split-caches), os diretórios também são particionados

- Normalmente as L3 são particionadas

- No exemplo a seguir, utilizaremos a L2 por questões de espaço

Diagrama de uma cache particionada

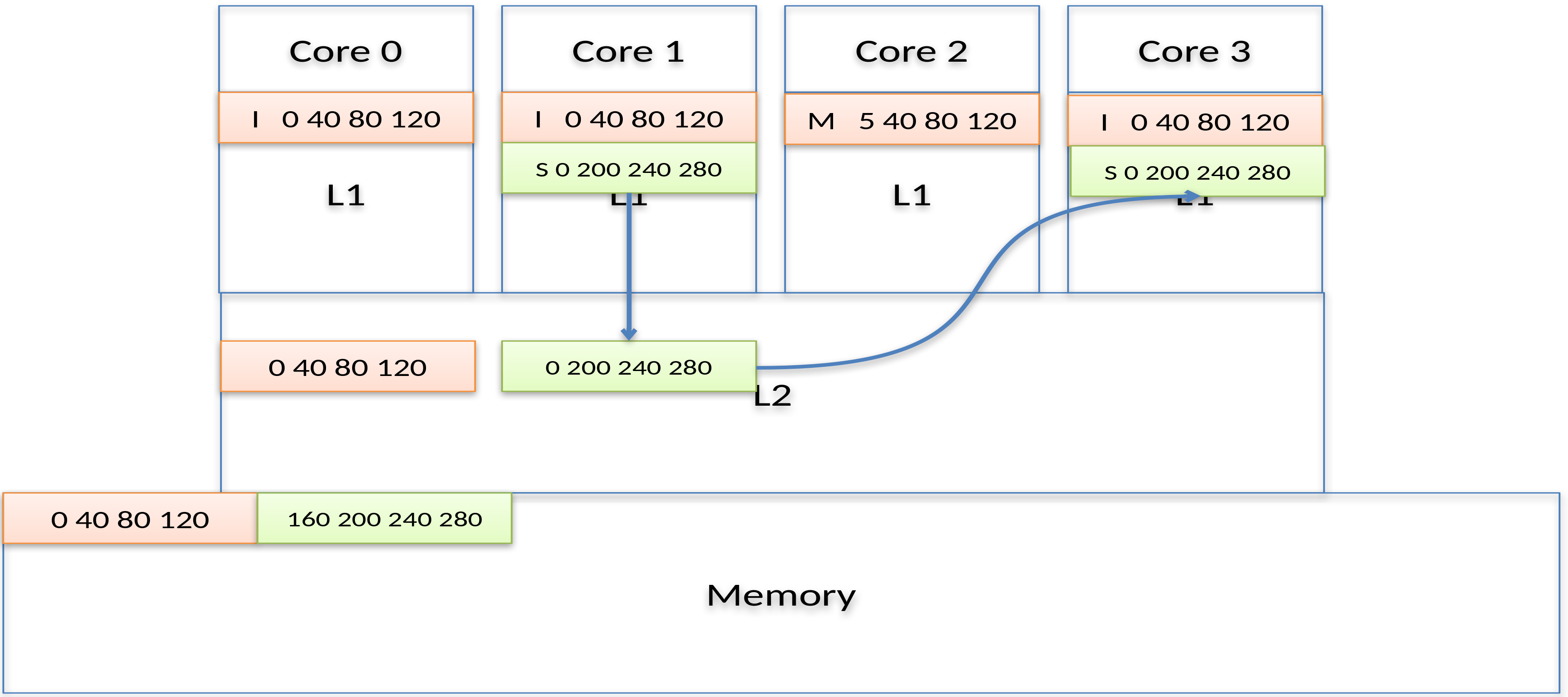

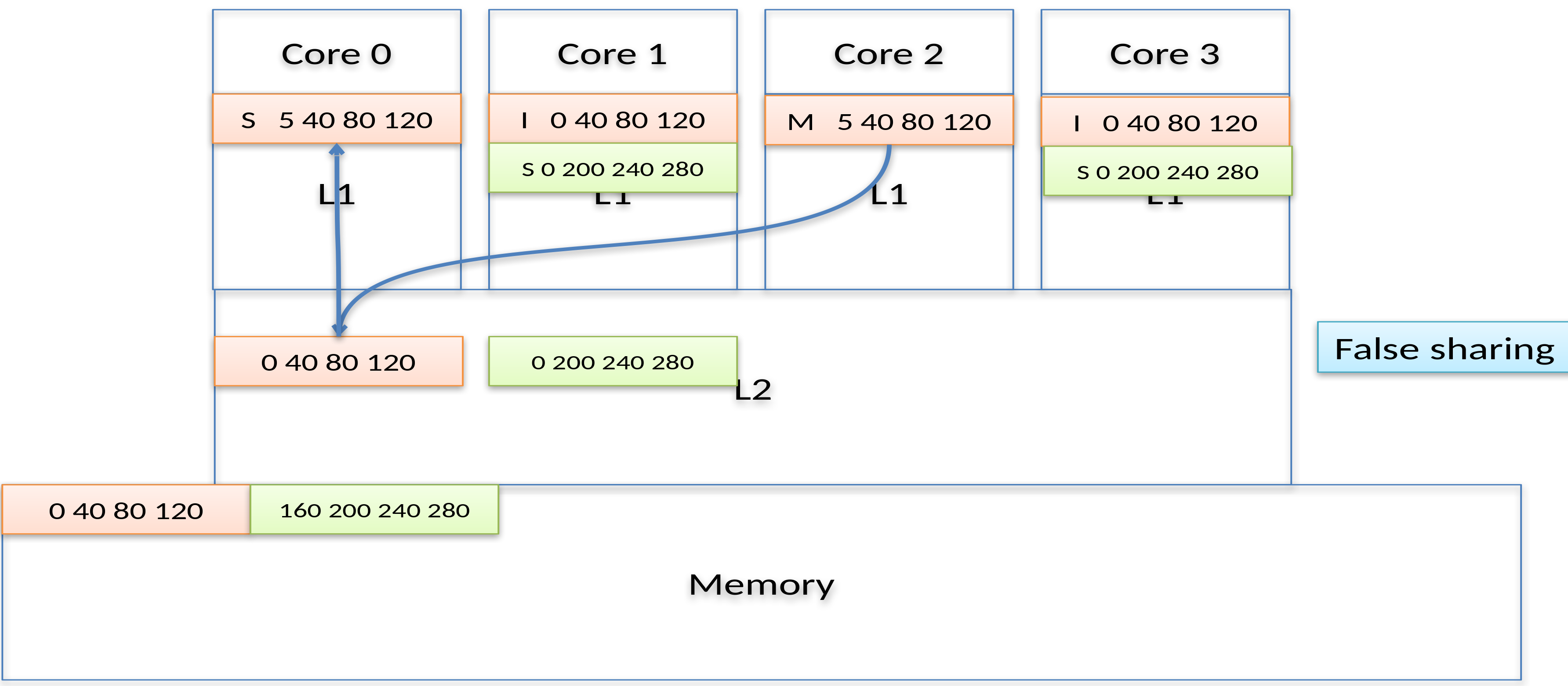

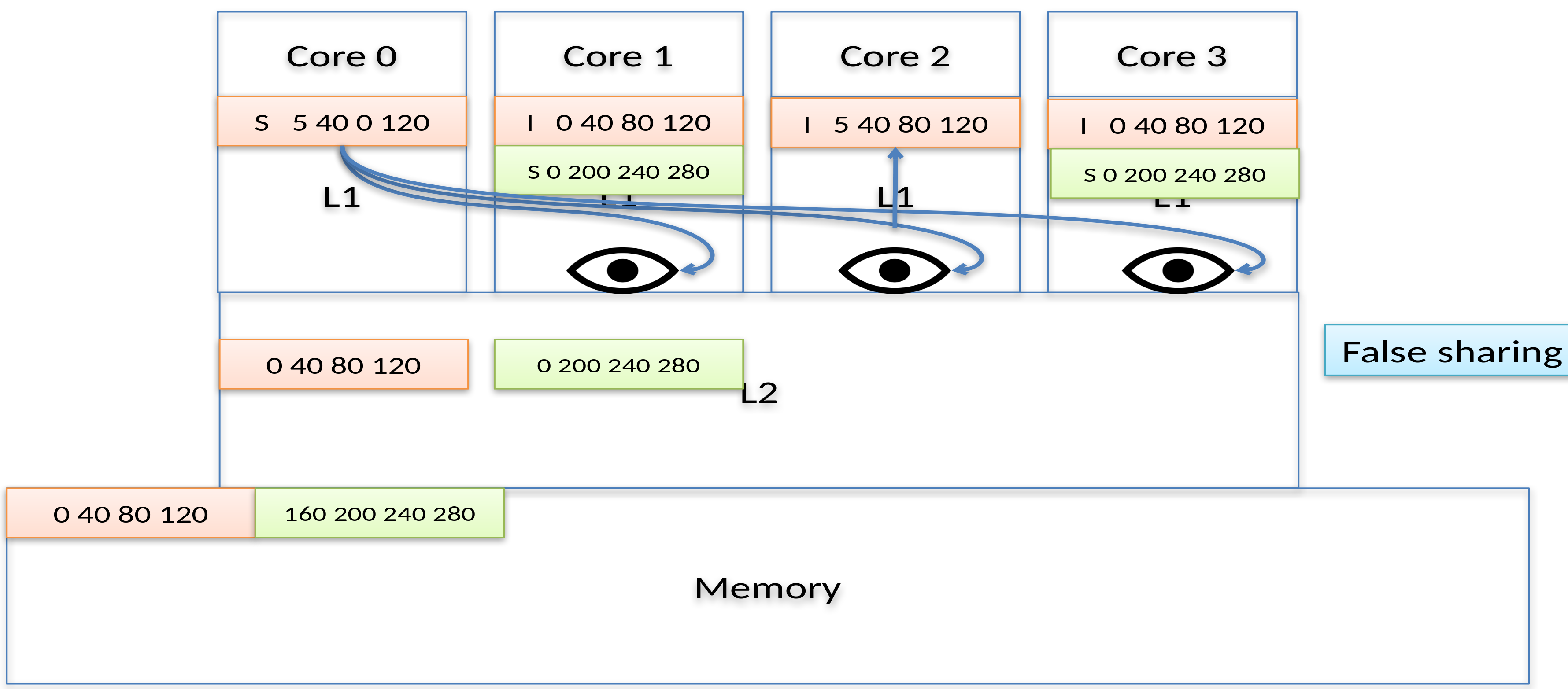

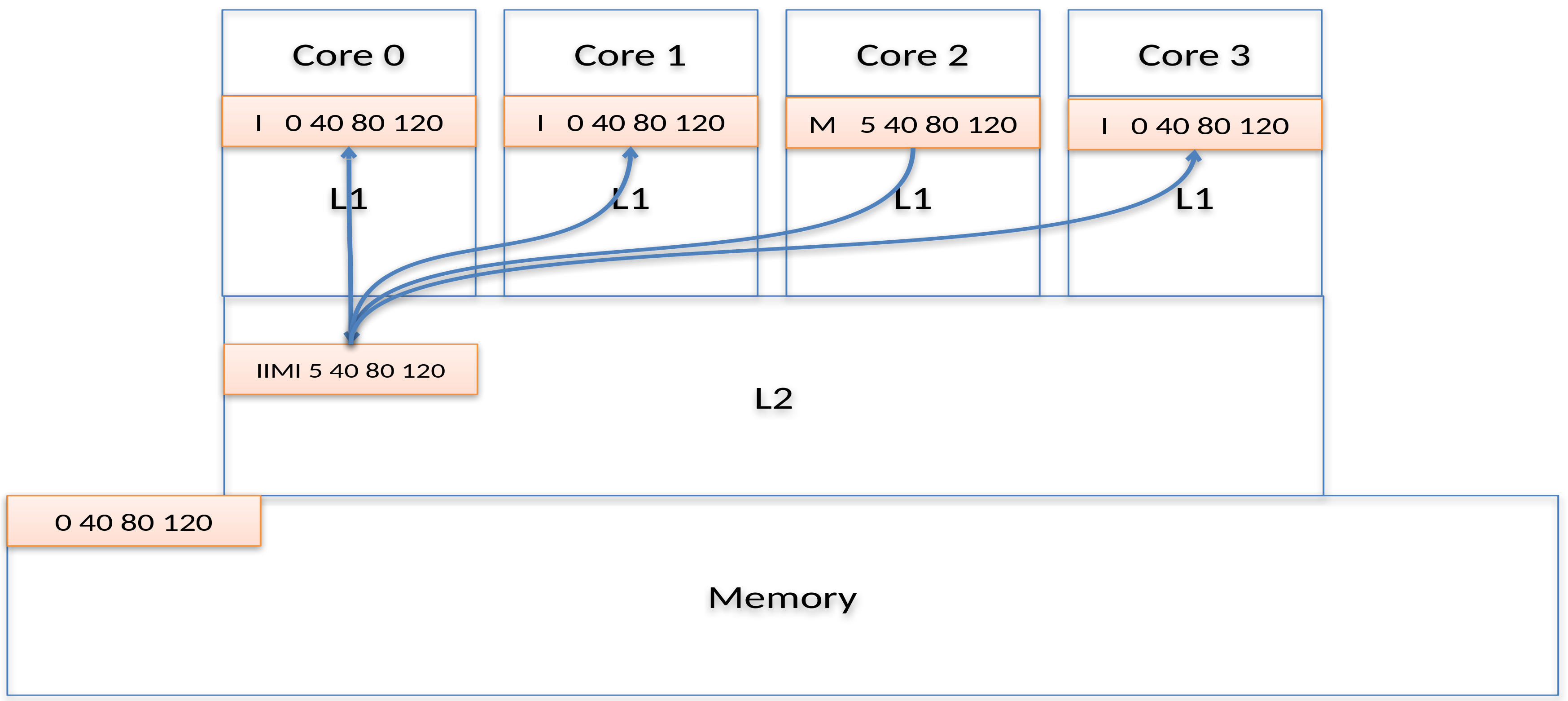

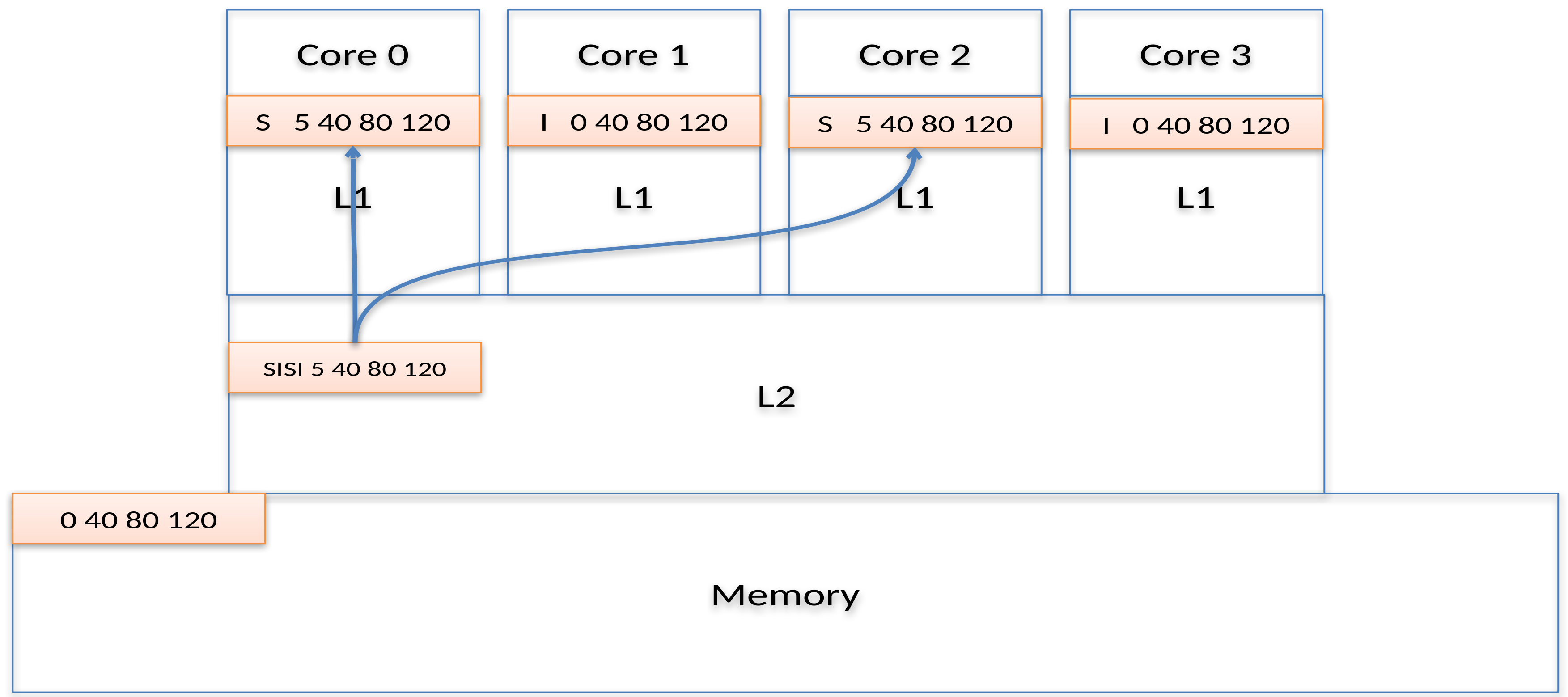

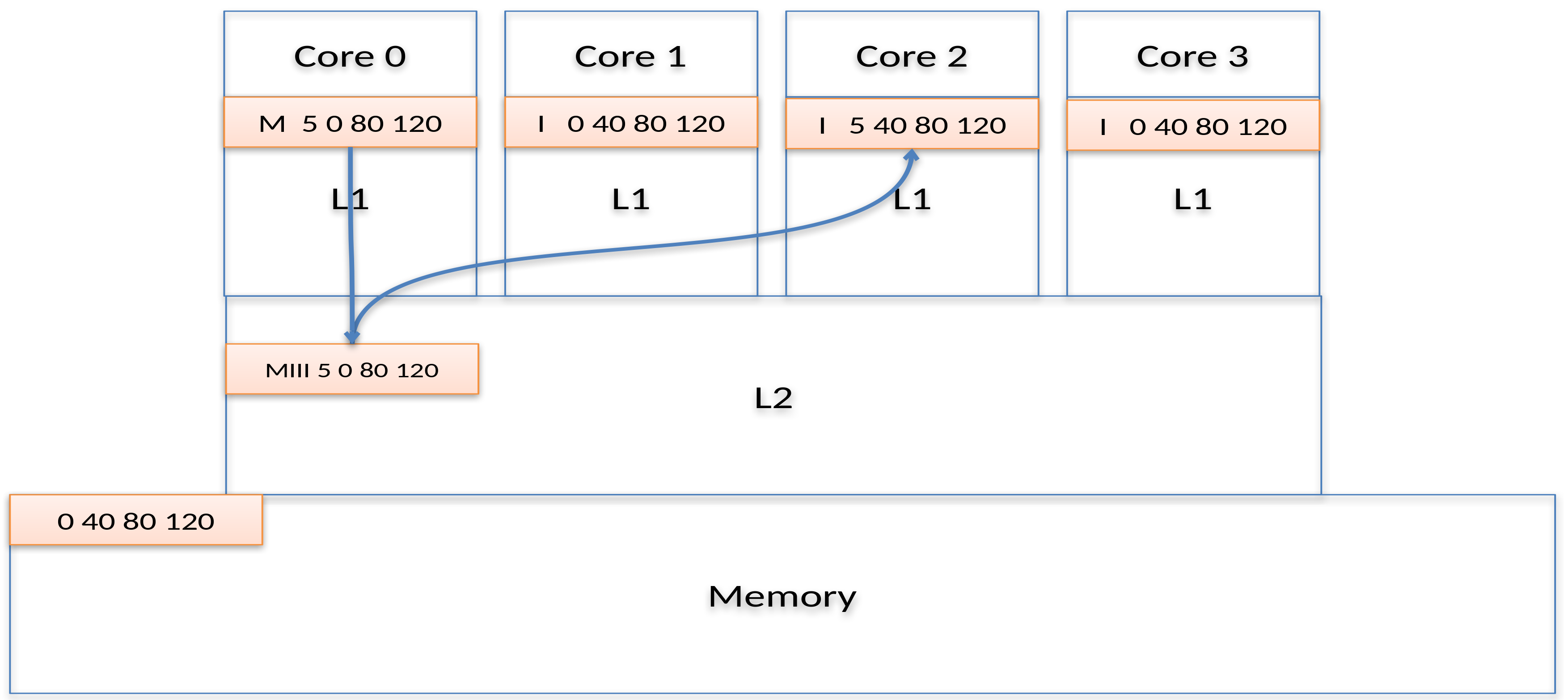

Protocolo MSI em diretório em ação

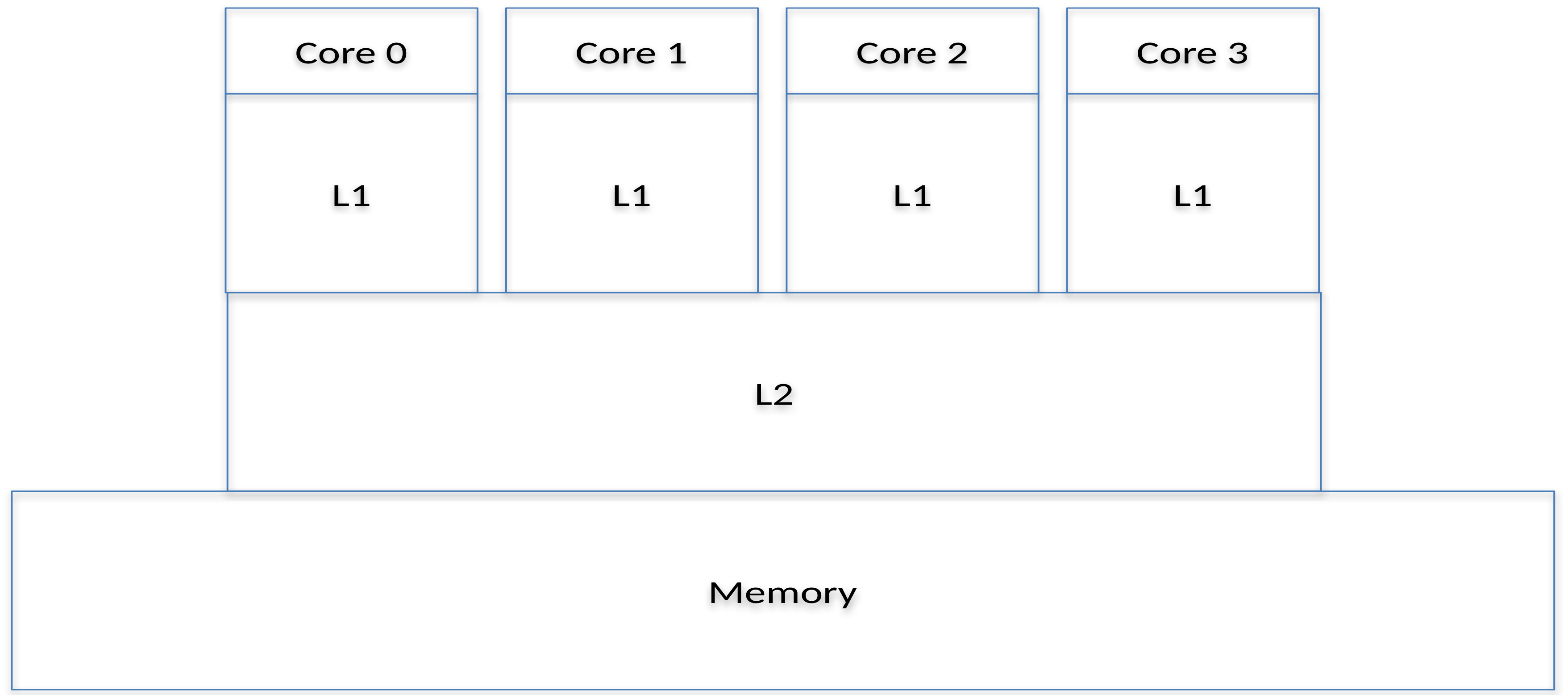

Considerando uma cache com:

- Bloco de 16 bytes

- Protocolo MSI

- Diretório

- Valores de memória

- Sistema com 4 cores, L1 privada, L2 compartilhada

- Diretório na L2

Diagrama do sistema

C0: READ(0);

C0: READ(0); C1: READ(0);

C0: READ(0); C1: READ(0); C2: READ(0); C3: READ(0);

C2: WRITE(0, 5);

C2: WRITE(0, 5); C0: READ(4);

C2: WRITE(0, 5); C0: READ(4); C0: WRITE(4, 0);

Outros Protocolos

- MESI

- Exclusive: bloco de cache possui o mesmo conteúdo que a memória e é a única cópia do dado

- MOSI

- Owned: múltiplas caches podem possuir o mesmo valor mas somente uma está no estado Owned. Essa cache pode responder requisições de leitura das demais

- MOESI

- Adiciona tanto Exclusive quanto Owned

Exercício: MESI

Exercício: MOSI

Exercício: MOESI