#### MC 613

IC/Unicamp 2013s1 Prof Guido Araújo Prof Mario Côrtes

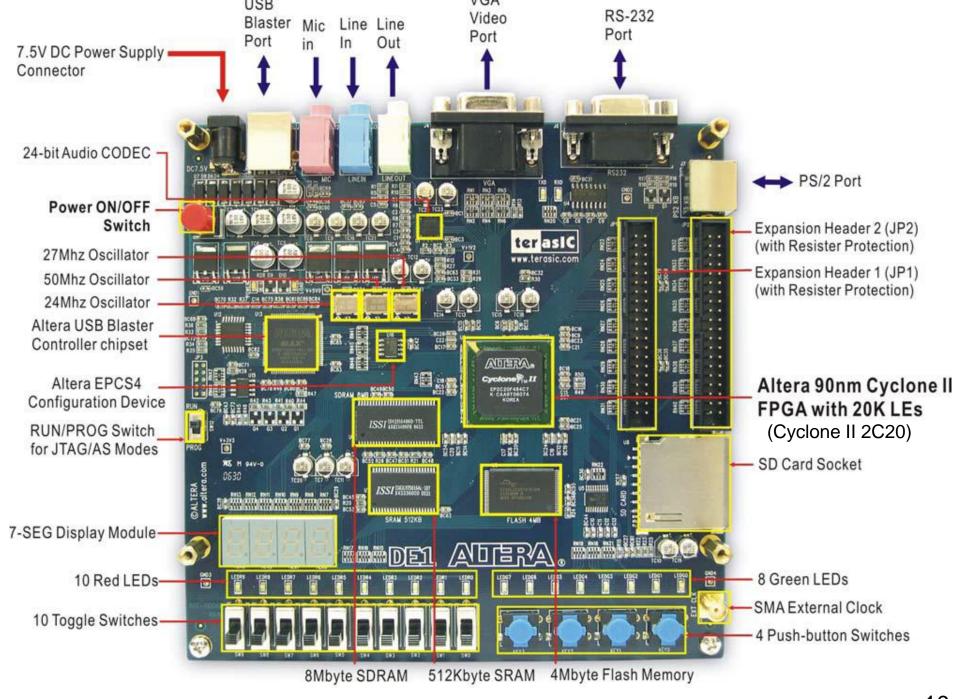

## Placa DE1 e FPGA Cyclone II

## **Tópicos**

- Dispositivos programáveis

- A FPGA Cyclone II

- A placa DE1

- Cuidados

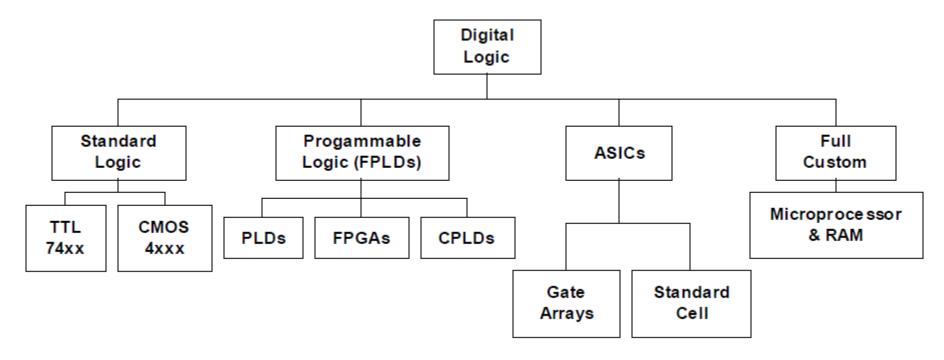

#### Implementações de circuitos digitais

- PLD: programmable logic device

- FPGA: field programmable gate array

- CPLD: complex programmable logic device

ASIC: application specific integrated circuit

#### Tipos de programação

#### Não volátil

- ROM: programação hardwired na fabricação

- PROM: programável uma vez em bancada: fusível queimado

- EPROM: apagável por ultra violeta e reprogramável na bancada

- EEPROM: programável eletricamente (condições elétricas especiais)

#### Volátil

Programação armazenada em registrador de deslocamento (SRAM) carregado no power-up

#### FPGA Cyclone II (2)

| Feature                                              | EP2C5   | EP2C8   | EP2C15  | EP2C20  | EP2C35  | EP2C50  | EP2C70        |

|------------------------------------------------------|---------|---------|---------|---------|---------|---------|---------------|

| LEs                                                  | 4,608   | 8,256   | 14,448  | 18,752  | 33,216  | 50,528  | 68,416        |

| M4K RAM<br>blocks (4Kbits<br>plus 512 parity<br>bits | 26      | 36      | 52      | 52      | 105     | 129     | 250           |

| Total RAM bits                                       | 119,808 | 165,888 | 239,616 | 239,616 | 483,840 | 594,432 | 1,152,00<br>0 |

| Embedded multipliers (3)                             | 13      | 18      | 26      | 26      | 35      | 86      | 150           |

| PLLs                                                 | 2       | 2       | 4       | 4       | 4       | 4       | 4             |

- Dispositivos programáveis voláteis (perdem a programação com suspensão da alimentação)

- organizados em LAB (logic array blocks), compostos por LE (logic elements) → ver datasheet\_cyclone2\_cii5v1\_01.pdf

# IC-UNICAMP

### FPGA Cyclone II (1)

- High-density architecture with 4,608 to 68,416 LEs

- M4K embedded memory blocks

- Up to 1.1 Mbits of RAM available without reducing available logic

- 4,096 memory bits per block (4,608 bits per block including 512 parity bits)

- Variable port configurations of ×1, ×2, ×4, ×8, ×9, ×16, ×18,

×32, and ×36

- True dual-port (one read and one write, two reads, or two writes) operation for ×1, ×2, ×4, ×8, ×9, ×16, and ×18 modes

- Byte enables for data input masking during writes

- Up to 260-MHz operation

- Embedded multipliers

- Up to 150 18- × 18-bit multipliers are each configurable as two independent 9- × 9-bit multipliers with up to 250-MHz performance

- Optional input and output registers

# IC-UNICAMP

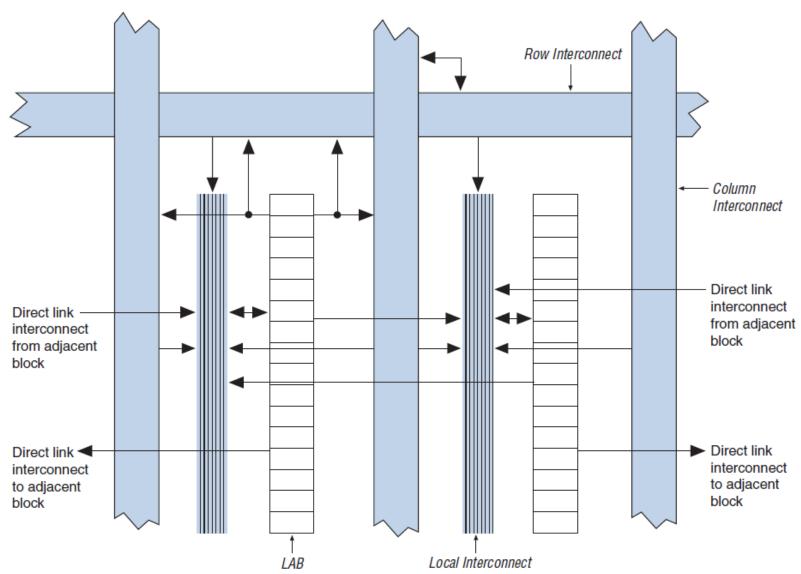

#### Arquitetura da FPGA Cyclone II

LAB: Logic Array Block (16 LEs: Logic Elements)

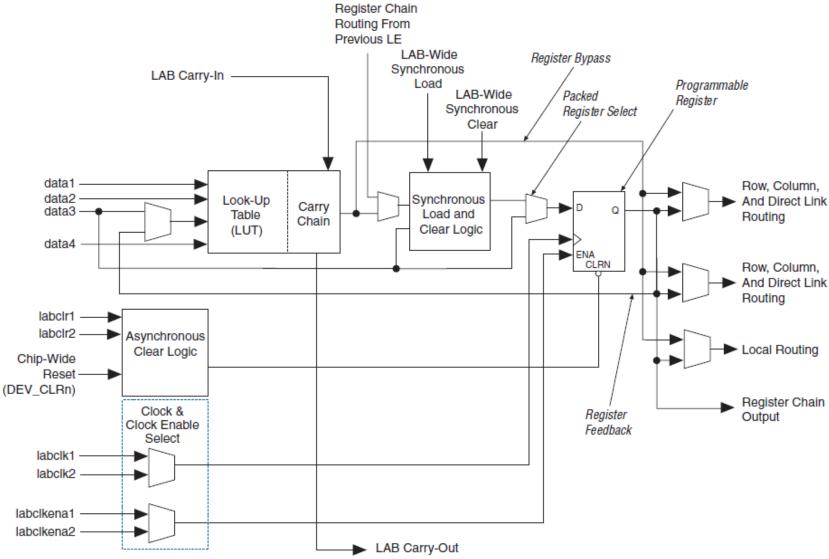

#### Os LEs (Logic Elements)

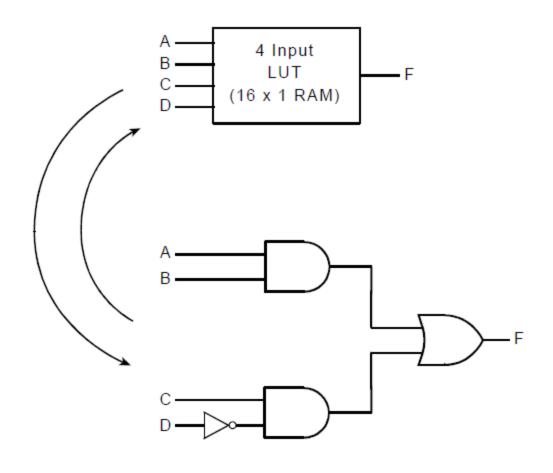

### As LUTs (Lookup Table)

| RAM Contents |     |      |                  |   |  |  |  |  |

|--------------|-----|------|------------------|---|--|--|--|--|

|              | Add | Data |                  |   |  |  |  |  |

| Α            | В   | С    | D                | F |  |  |  |  |

| A 0 0 0 0    | 0   | 0    | 0                | 0 |  |  |  |  |

| 0            | 0   | 0    | 0<br>1<br>0<br>1 |   |  |  |  |  |

| 0            | 0   | 1    | 0                | 1 |  |  |  |  |

| 0            | 0   | 1    | 1                | 0 |  |  |  |  |

| 0            | 1   | 0    | 0                | 0 |  |  |  |  |

| 0            | 1   | 0    | 1                | 0 |  |  |  |  |

| 0            | 1   | 1    | 0                | 1 |  |  |  |  |

| 0            | 1   | 1    | 1                | 0 |  |  |  |  |

| 1            | 0   | 0    | 1                | 0 |  |  |  |  |

| 1            | 0   | 0    | 1                | 0 |  |  |  |  |

| 1            | 0   | 1    | 0                | 1 |  |  |  |  |

| 1            | 0   | 1    | 1                | 0 |  |  |  |  |

| 1            | 1   | 0    | 0                | 1 |  |  |  |  |

| 1            | 1   | 0    | 1                | 1 |  |  |  |  |

| 1            | 1   | 1    | 0                | 1 |  |  |  |  |

| 1            | 1   | 1    | 1                | 1 |  |  |  |  |

VOA

#### Cuidados Básicos (ou seção Não ...)

Usar somente a fonte fornecida com o Kit

- Não usar outras fontes existentes no Laboratório

- Não conectar e desconectar fios, conectores (JTAG, ...) com a placa ligada

- Não colocar a placa sobre superfície metálica

- Segurar a placa pelas bordas

- Não colocar a mão nos componentes (problemas com eletricidade estática)

- Não retirar o kit do Laboratório (sala 305)

- Terminado o uso guardar o Kit no armário com todo o material acondicionado na respectiva caixa.

# Instalação do driver USB Blaster (tutorial tut\_initialDE1.pdf)

- 1. Ligue o cabo de alimentação e o cabo USB

- Ligue o botão On/Off

- 3. Caixa de diálogo: novo HW encontrado

- Informe que não deseja que o Windows procure o driver e que uma localização específica será fornecida

- 5. Indique o diretório como localização do driver:

- 1. C:\altera\91sp1\quartus\drivers\usb-blaster

#### Tutoriais a serem feitos pelo aluno

- tut\_initialDE1.pdf

- instalação do driver USB

- tut\_quartus\_intro\_schem.pdf

- introdução ao projeto com diagrama esquemático

- tut\_quartus\_intro\_vhdl.pdf

- introdução ao projeto com VHDL

- Simulação

- tut\_simulation\_vhdl.pdf (simulação funcional)

- tut\_timing\_vhdl.pdf (simulação com timing)