### MC613 – Laboratório de Circuitos Lógicos

# Laboratório 4

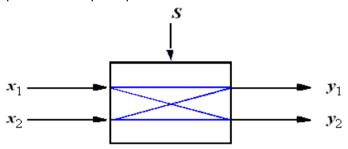

1. Seja o componente xbar que implementa um *crossbar switch*:

- a) Projete este circuito em VHDL usando a construção WITH, SELECT e WHEN [sem usar processo]. Verifique o funcionamento com simulação.

- b) Projete este mesmo circuito em VHDL usando a construção WHEN ELSE [sem usar processo]. Verifique o funcionamento com simulação.

- c) Projete este mesmo circuito em VHDL usando a construção PROCESS. Verifique o funcionamento com simulação.

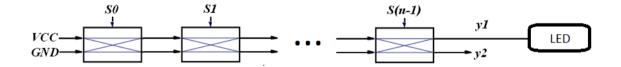

- d) A partir desse componente xbar implemente o circuito abaixo com número variável de estágios (utilize os comandos GENERIC e GENERATE).

- e) Crie um novo projeto instanciando este componente com 6 estágios. Programe a placa para verificar o funcionamento, usando 6 chaves (SW) e um LED como saída.

OBS - uma possível aplicação desse circuito: implementação de um número arbitrário de interruptores (S0..Sn-1) em um corredor longo, de modo que uma única mudança em qualquer dos interruptores muda o estado da iluminação (LED) de ligado para desligado ou vice-versa.

#### **ENTREGAR:**

- Q1a): Arquivos descrição VHDL (.vhd) e relatório de simulação (.cvwf)

- Q1b): Arquivos descrição VHDL (.vhd) e relatório de simulação (.cvwf)

- Q1c): Arquivos descrição VHDL (.vhd) e relatório de simulação (.cvwf)

- Q1e): Arquivos descrição VHDL (.vhd) do sistema completo

## MC613 – Laboratório de Circuitos Lógicos

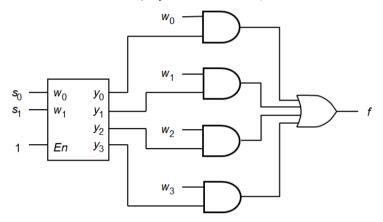

**2.** A figura abaixo mostra um circuito multiplexador 4 para 1 projetado utilizando-se um decodificador 2 para 4 e portas lógicas.  $w_{0..3}$  são as entradas,  $s_{0..1}$  os sinais de seleção de entrada, En sinal para ligar e desligar o circuito e f a saída selecionada. Verifique o funcionamento de todos os projetos com simulação.

Figura 1: Mux 4-1 usando Dec2-4 e gates

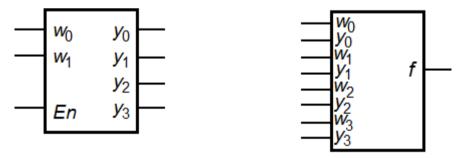

- a) Implemente o decodificador 2 para 4 em VHDL da Figura 2 [sem usar processo].

- b) Implemente o circuito dentro da caixa pontilhada na Figura 1, conforme o símbolo da Figura 3 [sem usar processo].

- c) A partir dos itens a e b, projete um multiplexador 4-1 como descrito na Figura 1.

- d) A partir do item c, implemente um multiplexador 16:1 em VHDL. Não deve ser usado processo nem implementado de forma estrutural (utilizando portas lógicas).

Figura 2: Dec2-4

Figura 3: Lógica extra

#### **ENTREGAR:**

- Q2a): Arquivos descrição VHDL (.vhd) e relatório de simulação (.cvwf)

- Q2b): Arquivos descrição VHDL (.vhd) e relatório de simulação (.cvwf)

- Q2c): Arquivos descrição VHDL (.vhd) e relatório de simulação (.cvwf)

- Q2d): Arquivos descrição VHDL (.vhd) e relatório de simulação (.cvwf)