# Software implementation of Post-Quantum Cryptography

Peter Schwabe

Radboud University Nijmegen, The Netherlands

October 20, 2013

ASCrypto 2013, Florianópolis, Brazil

# Part I

Optimizing cryptographic software with vector instructions

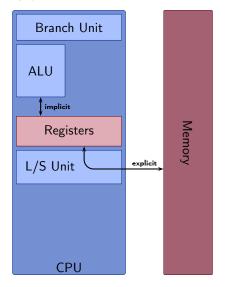

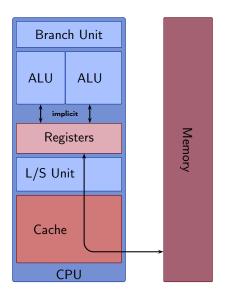

# Computers and computer programs

A highly simplified view

- ► A program is a sequence of instructions

- Load/Store instructions move data between memory and registers (processed by the L/S unit)

- Branch instructions (conditionally) jump to a position in the program

- Arithmetic instructions perform simple operations on values in registers (processed by the ALU)

- Registers are fast (fixed-size) storage units, addressed "by name"

#### A first program Adding up 1000 integers

- 1. Set register R1 to zero

- 2. Set register R2 to zero

- 3. Load 32-bits from address START+R2 into register R3

- 4. Add 32-bit integers in R1 and R3, write the result in R1

- 5. Increase value in register R2 by 4

- 6. Compare value in register R2 to 4000

- 7. Goto line 3 if R2 was smaller than 4000

# A first program

Adding up 1000 integers in readable syntax

```

int32 result

int32 tmp

int32 ctr

result = 0

ctr = 0

looptop:

tmp = mem32[START+ctr]

result += tmp

ctr += 4

unsigned<? ctr - 4000

goto looptop if unsigned<</pre>

```

- ► Easy approach: Per "time-slot" (*cycle*) execute one instruction, then go for the next

- Cycles needs to be long enough to finish the most complex supported instruction

- ► Easy approach: Per "time-slot" (cycle) execute one instruction, then go for the next

- Cycles needs to be long enough to finish the most complex supported instruction

- Other approach: Chop instructions into smaller tasks, e.g. for addition:

- 1. Fetch instruction

- 2. Decode instruction

- 3. Fetch register arguments

- 4. Execute (actual addition)

- 5. Write back to register

- ► Easy approach: Per "time-slot" (cycle) execute one instruction, then go for the next

- Cycles needs to be long enough to finish the most complex supported instruction

- Other approach: Chop instructions into smaller tasks, e.g. for addition:

- 1. Fetch instruction

- 2. Decode instruction

- 3. Fetch register arguments

- 4. Execute (actual addition)

- 5. Write back to register

- Overlap instructions (e.g., while one instruction is in step 2, the next one can do step 1 etc.)

- ▶ This is called pipelined execution (many more stages possible)

- Advantage: cycles can be much shorter (higher clock speed)

- ► Easy approach: Per "time-slot" (cycle) execute one instruction, then go for the next

- Cycles needs to be long enough to finish the most complex supported instruction

- Other approach: Chop instructions into smaller tasks, e.g. for addition:

- 1. Fetch instruction

- 2. Decode instruction

- 3. Fetch register arguments

- 4. Execute (actual addition)

- 5. Write back to register

- Overlap instructions (e.g., while one instruction is in step 2, the next one can do step 1 etc.)

- ► This is called pipelined execution (many more stages possible)

- Advantage: cycles can be much shorter (higher clock speed)

- ► Requirement for overlapping execution: instructions have to be independent

### Throughput and latency

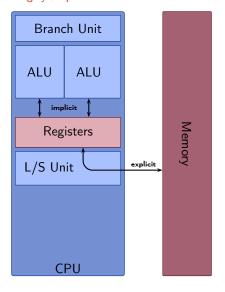

▶ While the ALU is executing an instruction the L/S and branch units are idle

#### Throughput and latency

- While the ALU is executing an instruction the L/S and branch units are idle

- ▶ Idea: Duplicate fetch and decode, handle two or three instructions per cycle

- ▶ While we're at it: Why not deploy two ALUs

- ▶ This concept is called *superscalar* execution

#### Throughput and latency

- While the ALU is executing an instruction the L/S and branch units are idle

- ▶ Idea: Duplicate fetch and decode, handle two or three instructions per cycle

- ▶ While we're at it: Why not deploy two ALUs

- ▶ This concept is called *superscalar* execution

- Number of independent instructions of one type per cycle: throughput

- Number of cycles that need to pass before the result can be used: latency

# An example computer Still highly simplified

- At most 4 instructions per cycle

- At most 1 Load/Store instruction per cycle

- At most 2 arithmetic instructions per cycle

- ► Arithmetic latency: 2 cycles

- ► Load latency: 3 cycles

- ► Branches have to be last instruction in a cycle

► Need at least 1000 load instructions: ≥ 1000 cycles

- ▶ At most 4 instructions per cycle

- At most 1 Load/Store instruction per cycle

- At most 2 arithmetic instructions per cycle

- Arithmetic latency: 2 cycles

- ► Load latency: 3 cycles

- Branches have to be last instruction in a cycle

- ► Need at least 1000 load instructions: ≥ 1000 cycles

- Need at least 999 addition instructions: ≥ 500 cycles

- ▶ At most 4 instructions per cycle

- At most 1 Load/Store instruction per cycle

- At most 2 arithmetic instructions per cycle

- Arithmetic latency: 2 cycles

- ► Load latency: 3 cycles

- Branches have to be last instruction in a cycle

- ► Need at least 1000 load instructions: ≥ 1000 cycles

- Need at least 999 addition instructions: ≥ 500 cycles

- ► At least 1999 instructions: ≥ 500 cycles

- ► At most 4 instructions per cycle

- At most 1 Load/Store instruction per cycle

- At most 2 arithmetic instructions per cycle

- Arithmetic latency: 2 cycles

- ► Load latency: 3 cycles

- Branches have to be last instruction in a cycle

- ► Need at least 1000 load instructions: ≥ 1000 cycles

- Need at least 999 addition instructions: ≥ 500 cycles

- ► At least 1999 instructions: ≥ 500 cycles

- ▶ Lower bound: 1000 cycles

- ▶ At most 4 instructions per cycle

- ► At most 1 Load/Store instruction per cycle

- At most 2 arithmetic instructions per cycle

- ► Arithmetic latency: 2 cycles

- ► Load latency: 3 cycles

- ► Branches have to be last instruction in a cycle

#### How about our program?

```

int32 result

int32 tmp

int32 ctr

result = 0

ctr = 0

looptop:

tmp = mem32[START+ctr]

result += tmp

ctr += 4

unsigned<? ctr - 4000

goto looptop if unsigned<</pre>

```

#### How about our program?

```

int32 result

int32 tmp

int32 ctr

result = 0

ctr = 0

looptop:

tmp = mem32[START+ctr]

# wait 2 cycles for tmp

result += tmp

ctr += 4

# wait 1 cycle for ctr

unsigned <? ctr - 4000

# wait 1 cycle for unsigned <

goto looptop if unsigned <

```

- Addition has to wait for load

- Comparison has to wait for addition

- Each iteration of the loop takes 8 cycles

- ► Total: > 8000 cycles

#### How about our program?

```

int32 result

int32 tmp

int32 ctr

result = 0

ctr = 0

looptop:

tmp = mem32[START+ctr]

# wait 2 cycles for tmp

result += tmp

ctr += 4

# wait 1 cycle for ctr

unsigned <? ctr - 4000

# wait 1 cycle for unsigned <

goto looptop if unsigned <

```

- Addition has to wait for load

- Comparison has to wait for addition

- Each iteration of the loop takes 8 cycles

- ► Total: > 8000 cycles

- ► This program sucks!

# Making the program fast Step 1 - Unrolling

```

result = 0

tmp = mem32[START+0]

result += tmp

tmp = mem32[START+4]

result += tmp

tmp = mem32[START+8]

result += tmp

...

tmp = mem32[START+3996]

result += tmp

```

Remove all the loop control: unrolling

# Making the program fast Step 1 - Unrolling

result = 0

```

tmp = mem32[START+0]

# wait 2 cycles for tmp

result += tmp

tmp = mem32[START+4]

# wait 2 cycles for tmp

result += tmp

tmp = mem32[START+8]

# wait 2 cycles for tmp

result += tmp

. . .

tmp = mem32[START+3996]

# wait 2 cycles for tmp

result += tmp

```

- Remove all the loop control: unrolling

- Each load-and-add now takes 3 cycles

- ▶ Total:  $\approx 3000$  cycles

# Making the program fast Step 1 - Unrolling

result = 0

```

tmp = mem32[START+0]

# wait 2 cycles for tmp

result += tmp

tmp = mem32[START+4]

# wait 2 cycles for tmp

result += tmp

tmp = mem32[START+8]

# wait 2 cycles for tmp

result += tmp

. . .

tmp = mem32[START+3996]

# wait 2 cycles for tmp

result += tmp

```

- Remove all the loop control: unrolling

- Each load-and-add now takes 3 cycles

- ▶ Total:  $\approx 3000$  cycles

- ▶ Better, but still too slow

# Making the program fast Step 2 – Instruction Scheduling

```

result = mem32[START + 0]

tmp0 = mem32[START + 4]

tmp1 = mem32[START + 8]

tmp2 = mem32[START +12]

result += tmp0

tmp0 = mem32[START+16]

result += tmp1

tmp1 = mem32[START+20]

result += tmp2

tmp2 = mem32[START+24]

result += tmp2

tmp2 = mem32[START+3996]

result += tmp0

result += tmp1

result += tmp2

```

- Load values earlier

- Load latencies are hidden

- Use more registers for loaded values (tmp0, tmp1, tmp2)

- ▶ Get rid of one addition to zero

# Making the program fast Step 2 – Instruction Scheduling

```

result = mem32[START + 0]

tmp0 = mem32[START + 4]

tmp1 = mem32[START + 8]

tmp2 = mem32[START +12]

result += tmp0

tmp0 = mem32[START+16]

# wait 1 cycle for result

result += tmp1

tmp1 = mem32[START+20]

# wait 1 cycle for result

result += tmp2

tmp2 = mem32[START+24]

. . .

result += tmp2

tmp2 = mem32[START+3996]

# wait 1 cycle for result

result += tmp0

# wait 1 cycle for result

```

# wait 1 cycle for result

result += tmp1

result += tmp2

- Load values earlier

- ► Load latencies are hidden

- ► Use more registers for loaded values (tmp0, tmp1, tmp2)

- ▶ Get rid of one addition to zero

- ▶ Now arithmetic latencies kick in

- ▶ Total:  $\approx 2000$  cycles

#### Making the program fast

Step 3 – More Instruction Scheduling (two accumulators)

```

result0 = mem32[START + 0]

tmp0 = mem32[START + 8]

result1 = mem32[START + 4]

tmp1 = mem32[START +12]

tmp2 = mem32[START +16]

result0 += tmp0

tmp0 = mem32[START+20]

result1 += tmp1

tmp1 = mem32[START+24]

result0 += tmp2

tmp2 = mem32[START+28]

. . .

result0 += tmp1

tmp1 = mem32[START+3996]

result1 += tmp2

result0 += tmp0

result1 += tmp1

result0 += result1

```

- Use one more accumulator register (result1)

- All latencies hidden

- ► Total: 1004 cycles

- Asymptotically n cycles for n additions

- ▶ Analyze the algorithm in terms of machine instructions

- ▶ Look at what the respective machine is able to do

- ► Compute a lower bound of the cycles

- ▶ Analyze the algorithm in terms of machine instructions

- ▶ Look at what the respective machine is able to do

- ► Compute a lower bound of the cycles

- Optimize until we (almost) reached the lower bound:

- ▶ Analyze the algorithm in terms of machine instructions

- ▶ Look at what the respective machine is able to do

- Compute a lower bound of the cycles

- ▶ Optimize until we (almost) reached the lower bound:

- Unroll the loop

- ▶ Analyze the algorithm in terms of machine instructions

- ▶ Look at what the respective machine is able to do

- ► Compute a lower bound of the cycles

- ▶ Optimize until we (almost) reached the lower bound:

- ▶ Unroll the loop

- Interleave independent instructions (instruction scheduling)

- ▶ Analyze the algorithm in terms of machine instructions

- ▶ Look at what the respective machine is able to do

- ► Compute a lower bound of the cycles

- ▶ Optimize until we (almost) reached the lower bound:

- ▶ Unroll the loop

- Interleave independent instructions (instruction scheduling)

- Resulting program is larger and requires more registers!

- ▶ Analyze the algorithm in terms of machine instructions

- ▶ Look at what the respective machine is able to do

- Compute a lower bound of the cycles

- ▶ Optimize until we (almost) reached the lower bound:

- ▶ Unroll the loop

- ► Interleave independent instructions (instruction scheduling)

- Resulting program is larger and requires more registers!

- ▶ Note: Good instruction scheduling typically requires more registers

- ▶ Analyze the algorithm in terms of machine instructions

- ▶ Look at what the respective machine is able to do

- Compute a lower bound of the cycles

- ▶ Optimize until we (almost) reached the lower bound:

- ▶ Unroll the loop

- ► Interleave independent instructions (instruction scheduling)

- Resulting program is larger and requires more registers!

- ▶ Note: Good instruction scheduling typically requires more registers

- ▶ Opposing requirements to **register allocation** (assigning registers to live variables, minimizing memory access)

- ▶ Analyze the algorithm in terms of machine instructions

- ▶ Look at what the respective machine is able to do

- ► Compute a lower bound of the cycles

- ▶ Optimize until we (almost) reached the lower bound:

- ► Unroll the loop

- ► Interleave independent instructions (instruction scheduling)

- Resulting program is larger and requires more registers!

- ▶ Note: Good instruction scheduling typically requires more registers

- ▶ Opposing requirements to **register allocation** (assigning registers to live variables, minimizing memory access)

- ▶ Both instruction scheduling and register allocation are NP hard

- ► So is the joint problem

- ▶ Many instances are efficiently solvable

#### Architectures and microarchitectures

#### What instructions and how many registers do we have?

- Instructions are defined by the instruction set

- Supported register names are defined by the set of architectural registers

- Instruction set and set of architectural registers together define the architecture

- Examples for architectures: x86, AMD64, ARMv6, ARMv7, UltraSPARC

- ► Sometimes base architectures are extended, e.g., MMX, SSE, NEON

#### Architectures and microarchitectures

#### What instructions and how many registers do we have?

- Instructions are defined by the instruction set

- Supported register names are defined by the set of architectural registers

- Instruction set and set of architectural registers together define the architecture

- Examples for architectures: x86, AMD64, ARMv6, ARMv7, UltraSPARC

- Sometimes base architectures are extended, e.g., MMX, SSE, NEON

#### What determines latencies etc?

- Different microarchitectures implement an architecture

- Latencies and throughputs are specific to a microarchitecture

- Example: Intel Core 2 Quad Q9550 implements the AMD64 architecture

- Optimal instruction scheduling depends on the microarchitecture

- Code optimized for one microarchitecture may run at very bad performance on another microarchitecture

- Many software is shipped in binary form (cannot recompile)

- Optimal instruction scheduling depends on the microarchitecture

- Code optimized for one microarchitecture may run at very bad performance on another microarchitecture

- ▶ Many software is shipped in binary form (cannot recompile)

- ▶ Idea: Let the processor reschedule instructions on the fly

- Look ahead a few instructions, pick one that can be executed

- ► This is called out-of-order execution

- Optimal instruction scheduling depends on the microarchitecture

- Code optimized for one microarchitecture may run at very bad performance on another microarchitecture

- Many software is shipped in binary form (cannot recompile)

- ▶ Idea: Let the processor reschedule instructions on the fly

- Look ahead a few instructions, pick one that can be executed

- ► This is called **out-of-order execution**

- ► Typically requires more physical than architectural registers and register renaming

- Optimal instruction scheduling depends on the microarchitecture

- Code optimized for one microarchitecture may run at very bad performance on another microarchitecture

- Many software is shipped in binary form (cannot recompile)

- ▶ Idea: Let the processor reschedule instructions on the fly

- Look ahead a few instructions, pick one that can be executed

- This is called out-of-order execution

- Typically requires more physical than architectural registers and register renaming

- ► Harder for the (assembly) programmer to understand what exactly will happen with the code

- Harder to come up with optimal scheduling

- Optimal instruction scheduling depends on the microarchitecture

- Code optimized for one microarchitecture may run at very bad performance on another microarchitecture

- Many software is shipped in binary form (cannot recompile)

- ▶ Idea: Let the processor reschedule instructions on the fly

- Look ahead a few instructions, pick one that can be executed

- This is called out-of-order execution

- Typically requires more physical than architectural registers and register renaming

- ► Harder for the (assembly) programmer to understand what exactly will happen with the code

- Harder to come up with optimal scheduling

- ► Harder to screw up completely

- ► So far there was nothing crypto-specific in this talk

- Is optimizing crypto the same as optimizing any other software?

- ► So far there was nothing crypto-specific in this talk

- ▶ Is optimizing crypto the same as optimizing any other software?

- ► No.

- ▶ So far there was nothing crypto-specific in this talk

- ▶ Is optimizing crypto the same as optimizing any other software?

- ▶ No. Cryptographic software deals with secret data (keys)

- ▶ Information about secret data must not leak through side channels

- ▶ So far there was nothing crypto-specific in this talk

- ▶ Is optimizing crypto the same as optimizing any other software?

- ▶ No. Cryptographic software deals with secret data (keys)

- ▶ Information about secret data must not leak through side channels

- ► Most critical for software implementations on "large" CPUs: software must take constant time (independent of secret data)

► Consider the following piece of code:

```

\begin{aligned} & \text{if } s \text{ then} \\ & r \leftarrow A \\ & \text{else} \\ & r \leftarrow B \\ & \text{end if} \end{aligned}

```

► Consider the following piece of code:

```

\begin{aligned} &\text{if } s \text{ then} \\ &r \leftarrow A \\ &\text{else} \\ &r \leftarrow B \\ &\text{end if} \end{aligned}

```

- ► General structure of any conditional branch

- $\blacktriangleright$  A and B can be large computations, r can be a large state

Consider the following piece of code:

```

\begin{array}{c} \textbf{if } s \textbf{ then} \\ r \leftarrow A \\ \textbf{else} \\ r \leftarrow B \\ \textbf{end if} \end{array}

```

- ► General structure of any conditional branch

- ▶ A and B can be large computations, r can be a large state

- ightharpoonup This code takes different amount of time, depending on s

- Obvious timing leak if s is secret

Consider the following piece of code:

```

\begin{aligned} &\text{if } s \text{ then} \\ &r \leftarrow A \\ &\text{else} \\ &r \leftarrow B \\ &\text{end if} \end{aligned}

```

- General structure of any conditional branch

- A and B can be large computations, r can be a large state

- lacktriangle This code takes different amount of time, depending on s

- Obvious timing leak if s is secret

- Even if A and B take the same amount of cycles this is not constant time!

- Reason: Conditional branch takes different amount of cycles whether taken or not

- ► Never use secret-data-dependent branch conditions

end if

▶ So, what do we do with this piece of code? if s then  $r \leftarrow A$  else  $r \leftarrow B$

► So, what do we do with this piece of code?

$$\begin{aligned} & \text{if } s \text{ then} \\ & r \leftarrow A \\ & \text{else} \\ & r \leftarrow B \\ & \text{end if} \end{aligned}$$

► Replace by

$$r \leftarrow sA + (1-s)B$$

▶ So, what do we do with this piece of code?

$$\begin{aligned} & \text{if } s \text{ then} \\ & r \leftarrow A \\ & \text{else} \\ & r \leftarrow B \\ & \text{end if} \end{aligned}$$

Replace by

$$r \leftarrow sA + (1-s)B$$

ightharpoonup Can expand s to all-one/all-zero mask and use XOR instead of addition, AND instead of multiplication

▶ So, what do we do with this piece of code?

$$\begin{array}{c} \textbf{if } s \textbf{ then} \\ r \leftarrow A \\ \textbf{else} \\ r \leftarrow B \\ \textbf{end if} \end{array}$$

Replace by

$$r \leftarrow sA + (1-s)B$$

- ightharpoonup Can expand s to all-one/all-zero mask and use XOR instead of addition, AND instead of multiplication

- ▶ For very fast A and B this can even be faster

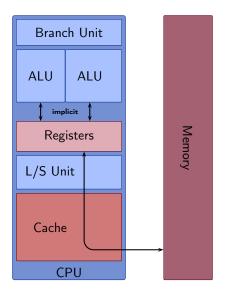

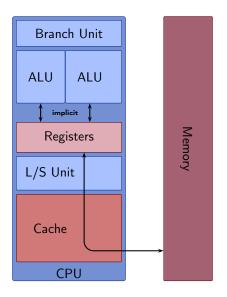

### Cached memory access

- Memory access goes through a cache

- Small but fast transparent memory for frequently used data

### Cached memory access

- Memory access goes through a cache

- Small but fast transparent memory for frequently used data

- ► A load from memory places data also in the cache

- Data remains in cache until it's replaced by other data

## Cached memory access

- Memory access goes through a cache

- Small but fast transparent memory for frequently used data

- ► A load from memory places data also in the cache

- Data remains in cache until it's replaced by other data

- Loading data is fast if data is in the cache (cache hit)

- Loading data is slow if data is not in the cache (cache miss)

| $T[0] \dots T[15]$    |

|-----------------------|

| $T[16] \dots T[31]$   |

| $T[32] \dots T[47]$   |

| $T[48] \dots T[63]$   |

| $T[64] \dots T[79]$   |

| $T[80] \dots T[95]$   |

| $T[96] \dots T[111]$  |

| $T[112] \dots T[127]$ |

| $T[128] \dots T[143]$ |

| $T[144] \dots T[159]$ |

| $T[160] \dots T[175]$ |

| $T[176] \dots T[191]$ |

| $T[192] \dots T[207]$ |

| $T[208] \dots T[223]$ |

| $T[224] \dots T[239]$ |

| $T[240] \dots T[255]$ |

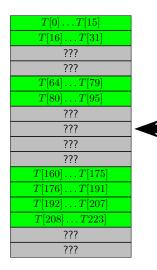

- ► Consider lookup table of 32-bit integers

- ► Cache lines have 64 bytes

- Crypto and the attacker's program run on the same CPU

- ► Tables are in cache

| $T[0] \dots T[15]$    |

|-----------------------|

| $T[16] \dots T[31]$   |

| attacker's data       |

| attacker's data       |

| $T[64] \dots T[79]$   |

| $T[80] \dots T[95]$   |

| attacker's data       |

| attacker's data       |

| attacker's data       |

| attacker's data       |

| $T[160] \dots T[175]$ |

| $T[176] \dots T[191]$ |

| $T[192] \dots T[207]$ |

| $T[208] \dots T[223]$ |

| attacker's data       |

| attacker's data       |

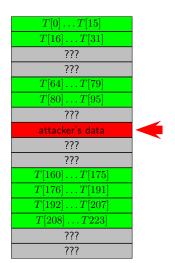

- Consider lookup table of 32-bit integers

- ► Cache lines have 64 bytes

- Crypto and the attacker's program run on the same CPU

- ► Tables are in cache

- ► The attacker's program replaces some cache lines

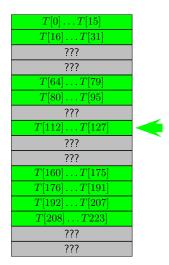

| $T[0] \dots T[15]$    |

|-----------------------|

| $T[16] \dots T[31]$   |

| ???                   |

| ???                   |

| $T[64] \dots T[79]$   |

| $T[80] \dots T[95]$   |

| ???                   |

| ???                   |

| ???                   |

| ???                   |

| $T[160] \dots T[175]$ |

| $T[176] \dots T[191]$ |

| $T[192] \dots T[207]$ |

| $T[208] \dots T223]$  |

| ???                   |

| ???                   |

- ► Consider lookup table of 32-bit integers

- ► Cache lines have 64 bytes

- Crypto and the attacker's program run on the same CPU

- Tables are in cache

- The attacker's program replaces some cache lines

- Crypto continues, loads from table again

- ► Consider lookup table of 32-bit integers

- ► Cache lines have 64 bytes

- Crypto and the attacker's program run on the same CPU

- Tables are in cache

- The attacker's program replaces some cache lines

- Crypto continues, loads from table again

- ► Attacker loads his data:

- ► Consider lookup table of 32-bit integers

- ► Cache lines have 64 bytes

- Crypto and the attacker's program run on the same CPU

- Tables are in cache

- The attacker's program replaces some cache lines

- Crypto continues, loads from table again

- Attacker loads his data:

- Fast: cache hit (crypto did not just load from this line)

- ► Consider lookup table of 32-bit integers

- ► Cache lines have 64 bytes

- Crypto and the attacker's program run on the same CPU

- Tables are in cache

- The attacker's program replaces some cache lines

- Crypto continues, loads from table again

- Attacker loads his data:

- Fast: cache hit (crypto did not just load from this line)

- Slow: cache miss (crypto just loaded from this line)

▶ This is only the *most basic* cache-timing attack

- ▶ This is only the *most basic* cache-timing attack

- ▶ Non-secret cache lines are not enough for security

- ► Load/Store addresses influence timing in many different ways

- ▶ Do not access memory at secret-data-dependent addresses

- ▶ This is only the *most basic* cache-timing attack

- Non-secret cache lines are not enough for security

- ► Load/Store addresses influence timing in many different ways

- ▶ Do not access memory at secret-data-dependent addresses

- Timing attacks are practical:

Osvik, Tromer, Shamir, 2006: 65 ms to steal a 256-bit AES key used for Linux hard-disk encryption

- ▶ This is only the *most basic* cache-timing attack

- Non-secret cache lines are not enough for security

- ► Load/Store addresses influence timing in many different ways

- ▶ Do not access memory at secret-data-dependent addresses

- Timing attacks are practical:

Osvik, Tromer, Shamir, 2006: 65 ms to steal a 256-bit AES key used for Linux hard-disk encryption

- Remote timing attacks are practical:

Brumley, Tuveri, 2011: A few minutes to steal ECDSA signing key from OpenSSL implementation

lacktriangle Want to load item at (secret) position p from table of size n

- lackbox Want to load item at (secret) position p from table of size n

- ▶ Load all items, use arithmetic to pick the right one:

```

\begin{array}{l} \textbf{for} \ i \ \mathsf{from} \ 0 \ \mathsf{to} \ n-1 \ \textbf{do} \\ d \leftarrow T[i] \\ \textbf{if} \ p = i \ \textbf{then} \\ r \leftarrow d \\ \textbf{end} \ \textbf{if} \\ \textbf{end} \ \textbf{for} \end{array}

```

- lacktriangle Want to load item at (secret) position p from table of size n

- ▶ Load all items, use arithmetic to pick the right one:

```

\begin{aligned} & \textbf{for} \ i \ \text{from} \ 0 \ \text{to} \ n-1 \ \textbf{do} \\ & d \leftarrow T[i] \\ & \textbf{if} \ p=i \ \textbf{then} \\ & r \leftarrow d \\ & \textbf{end} \ \textbf{if} \end{aligned}

```

▶ Problem 1: if-statements are not constant time (see before)

- ▶ Want to load item at (secret) position *p* from table of size *n*

- ▶ Load all items, use arithmetic to pick the right one:

```

\begin{array}{c} \textbf{for} \ i \ \mathsf{from} \ 0 \ \mathsf{to} \ n-1 \ \textbf{do} \\ d \leftarrow T[i] \\ \textbf{if} \ p = i \ \textbf{then} \\ r \leftarrow d \\ \textbf{end} \ \textbf{if} \\ \textbf{end} \ \textbf{for} \end{array}

```

- ▶ Problem 1: if-statements are not constant time (see before)

- Problem 2: Comparisons are not constant time, replace by:

```

static unsigned long long eq(uint32_t a, uint32_t b)

{

unsigned long long t = a ^ b;

t = (-t) >> 63;

return 1-t;

}

```

► Are secret branch conditions and secret load/store addresses the only problem?

- Are secret branch conditions and secret load/store addresses the only problem?

- Answer by Langley: "That's assuming that the fundamental processor instructions are constant time, but that's true for all sane CPUs."

## Timing leakage part III

- Are secret branch conditions and secret load/store addresses the only problem?

- Answer by Langley: "That's assuming that the fundamental processor instructions are constant time, but that's true for all sane CPUs."

- ▶ Some architectures have *non-constant-time* arithmetic

- Examples:

- ▶ UMULL/SMULL and UMLAL/SMLAL on ARM Cortex-M3

- DIV instruction on Intel processors, see also https:

- //www.imperialviolet.org/2013/02/04/luckythirteen.html

## Timing leakage part III

- Are secret branch conditions and secret load/store addresses the only problem?

- Answer by Langley: "That's assuming that the fundamental processor instructions are constant time, but that's true for all sane CPUs."

- ▶ Some architectures have *non-constant-time* arithmetic

- Examples:

- ▶ UMULL/SMULL and UMLAL/SMLAL on ARM Cortex-M3

- DIV instruction on Intel processors, see also https:

```

//www.imperialviolet.org/2013/02/04/luckythirteen.html

```

#### Summary

- ▶ Writing efficient constant-time code is hard

- ▶ Typically requires reconsiderations through all optimization levels

#### SIMD computations

"Thus we arbitrarily select a reference organization: the IBM 704-70927090. This organization is then regarded as the prototype of the class of machines which we label:

1) Single Instruction Stream-Single Data Stream (SISD).

Three additional organizational classes are evident.

- 2) Single Instruction Stream-Multiple Data Stream (SIMD)

- 3) Multiple Instruction Stream-Single Data Stream (MISD)

- 4) Multiple Instruction Stream-Multiple Data Stream (MIMD)"

- Michael J. Flynn. Very high-speed computing systems. 1966.

# SISD

Example: 32-bit integer addition

```

int64 a

int64 b

a = mem32[addr1 + 0]

b = mem32[addr2 + 0]

(uint32) a += b

mem32[addr3 + 0] = a

```

#### SIMD with vector instructions

Example: 4 32-bit integer additions

```

reg128 a

reg128 b

a = mem128[addr1 + 0]

b = mem128[addr2 + 0]

4x a += b

mem128[addr3 + 0] = a

```

# Back to adding 1000 integers

- ▶ Imagine that

- vector addition is as fast as scalar addition

- vector loads are as fast as scalar loads

## Back to adding 1000 integers

- Imagine that

- vector addition is as fast as scalar addition

- vector loads are as fast as scalar loads

- ▶ Need only 250 vector additions, 250 vector loads

- ▶ Lower bound of 250 cycles

# Back to adding 1000 integers

- Imagine that

- vector addition is as fast as scalar addition

- vector loads are as fast as scalar loads

- ▶ Need only 250 vector additions, 250 vector loads

- ▶ Lower bound of 250 cycles

- Very straight-forward modification of the program

- $\blacktriangleright$  Fully unrolled loop needs only 1/4 of the space

► Consider the Intel Nehalem processor

- ► Consider the Intel Nehalem processor

- ▶ 32-bit load throughput: 1 per cycle

- ▶ 32-bit add throughput: 3 per cycle

- ▶ 32-bit store throughput: 1 per cycle

- Consider the Intel Nehalem processor

- ▶ 32-bit load throughput: 1 per cycle

- ▶ 32-bit add throughput: 3 per cycle

- ▶ 32-bit store throughput: 1 per cycle

- ▶ 128-bit load throughput: 1 per cycle

- ▶ 4× 32-bit add throughput: 2 per cycle

- ▶ 128-bit store throughput: 1 per cycle

- Consider the Intel Nehalem processor

- ▶ 32-bit load throughput: 1 per cycle

- ▶ 32-bit add throughput: 3 per cycle

- ▶ 32-bit store throughput: 1 per cycle

- ▶ 128-bit load throughput: 1 per cycle

- ► 4× 32-bit add throughput: 2 per cycle

- 128-bit store throughput: 1 per cycle

- Vector instructions are almost as fast as scalar instructions but do 4× the work

- Consider the Intel Nehalem processor

- 32-bit load throughput: 1 per cycle

- 32-bit add throughput: 3 per cycle

- ▶ 32-bit store throughput: 1 per cycle

- ▶ 128-bit load throughput: 1 per cycle

- ► 4× 32-bit add throughput: 2 per cycle

- 128-bit store throughput: 1 per cycle

- $\blacktriangleright$  Vector instructions are almost as fast as scalar instructions but do  $4\times$  the work

- Situation on other architectures/microarchitectures is similar

- Reason: cheap way to increase arithmetic throughput (less decoding, address computation, etc.)

## More reasons for using vector arithmetic

- ▶ Data-dependent branches are expensive in SIMD

- Variably indexed loads (lookups) into vectors are expensive

- ▶ Need to rewrite algorithms to eliminate branches and lookups

## More reasons for using vector arithmetic

- ▶ Data-dependent branches are expensive in SIMD

- ▶ Variably indexed loads (lookups) into vectors are expensive

- Need to rewrite algorithms to eliminate branches and lookups

- Secret-data-dependent branches and secret branch conditions are the major sources of timing-attack vulnerabilities

## More reasons for using vector arithmetic

- Data-dependent branches are expensive in SIMD

- Variably indexed loads (lookups) into vectors are expensive

- ▶ Need to rewrite algorithms to eliminate branches and lookups

- Secret-data-dependent branches and secret branch conditions are the major sources of timing-attack vulnerabilities

- Strong synergies between speeding up code with vector instructions and protecting code!

- ► When adding two 32-bit integers, the result may have 33 bits (32-bit result + carry)

- ▶ Scalar additions keep the carry in a special flag register

- ► Subsequent instructions can use this flag, e.g., "add with carry"

- ► When adding two 32-bit integers, the result may have 33 bits (32-bit result + carry)

- ▶ Scalar additions keep the carry in a special flag register

- ► Subsequent instructions can use this flag, e.g., "add with carry"

- ► How about carries of vector additions?

- ► Answer 1: Special "carry generate" instruction (e.g., CBE-SPU)

- ► When adding two 32-bit integers, the result may have 33 bits (32-bit result + carry)

- ▶ Scalar additions keep the carry in a special flag register

- ► Subsequent instructions can use this flag, e.g., "add with carry"

- ► How about carries of vector additions?

- ► Answer 1: Special "carry generate" instruction (e.g., CBE-SPU)

- Answer 2: They're lost, recomputation is very expensive

- ► When adding two 32-bit integers, the result may have 33 bits (32-bit result + carry)

- ▶ Scalar additions keep the carry in a special flag register

- ► Subsequent instructions can use this flag, e.g., "add with carry"

- ► How about carries of vector additions?

- ► Answer 1: Special "carry generate" instruction (e.g., CBE-SPU)

- ► Answer 2: They're lost, recomputation is very expensive

- ▶ Need to avoid carries instead of handling them

- No problem for today's talk, but requires care for big-integer arithmetic

- ▶ If we don't vectorize we perform multiple independent instructions

- ► We turn data-level parallelism (DLP) into instruction-level parallelism (ILP)

- ▶ If we don't vectorize we perform multiple independent instructions

- ► We turn data-level parallelism (DLP) into instruction-level parallelism (ILP)

- ▶ Pipelined and multiscalar execution need ILP

- Vectorization removes ILP

- ▶ Problematic for algorithms with, e.g., 4-way DLP

- ▶ If we don't vectorize we perform multiple independent instructions

- ► We turn data-level parallelism (DLP) into instruction-level parallelism (ILP)

- Pipelined and multiscalar execution need ILP

- Vectorization removes ILP

- ▶ Problematic for algorithms with, e.g., 4-way DLP

- ► Good example to see this: ChaCha/Salsa/Blake

- ▶ If we don't vectorize we perform multiple independent instructions

- ► We turn data-level parallelism (DLP) into instruction-level parallelism (ILP)

- Pipelined and multiscalar execution need ILP

- Vectorization removes ILP

- ▶ Problematic for algorithms with, e.g., 4-way DLP

- ► Good example to see this: ChaCha/Salsa/Blake

- Vectorization of ChaCha and Salsa can resort to higher-level parallelism (multiple blocks)

- ▶ Harder for Blake: each block depends on the previous one

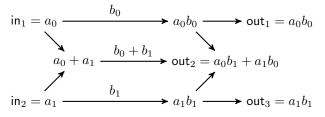

#### Data shuffeling

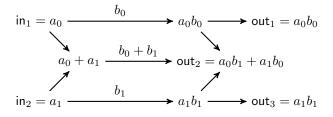

Consider multiplication of 4-coefficient polynomials  $f = f_0 + f_1x + f_2x^2 + f_3x^3$  and  $q = q_0 + q_1x + q_2x^2 + q_3x^3$ :

$$r_0 = f_0 g_0$$

$$r_1 = f_0 g_1 + f_1 g_0$$

$$r_2 = f_0 g_2 + f_1 g_1 + f_2 g_0$$

$$r_3 = f_0 g_3 + f_1 g_2 + f_2 g_1 + f_3 g_0$$

$$r_4 = f_1 g_3 + f_2 g_2 + f_3 g_1$$

$$r_5 = f_2 g_3 + f_3 g_2$$

$$r_6 = f_3 g_3$$

#### Data shuffeling

Consider multiplication of 4-coefficient polynomials  $f = f_0 + f_1 x + f_2 x^2 + f_3 x^3$  and  $g = g_0 + g_1 x + g_2 x^2 + g_3 x^3$ :

$$r_0 = f_0 g_0$$

$$r_1 = f_0 g_1 + f_1 g_0$$

$$r_2 = f_0 g_2 + f_1 g_1 + f_2 g_0$$

$$r_3 = f_0 g_3 + f_1 g_2 + f_2 g_1 + f_3 g_0$$

$$r_4 = f_1 g_3 + f_2 g_2 + f_3 g_1$$

$$r_5 = f_2 g_3 + f_3 g_2$$

$$r_6 = f_3 g_3$$

- ▶ Ignore carries, overflows etc. for a moment

- ▶ 16 multiplications, 9 additions

- ► How to vectorize multiplications?

#### Data shuffeling

$$\begin{split} r_0 &= f_0 g_0 \\ r_1 &= f_0 g_1 + f_1 g_0 \\ r_2 &= f_0 g_2 + f_1 g_1 + f_2 g_0 \\ r_3 &= f_0 g_3 + f_1 g_2 + f_2 g_1 + f_3 g_0 \\ r_4 &= f_1 g_3 + f_2 g_2 + f_3 g_1 \\ r_5 &= f_2 g_3 + f_3 g_2 \\ r_6 &= f_3 g_3 \end{split}$$

- ► Can easily load  $(f_0, f_1, f_2, f_3)$  and  $(g_0, g_1, g_2, g_3)$

- ► Multiply, obtain  $(f_0g_0, f_1g_1, f_2g_2, f_3g_3)$

#### Data shuffeling

$$\begin{split} r_0 &= f_0 g_0 \\ r_1 &= f_0 g_1 + f_1 g_0 \\ r_2 &= f_0 g_2 + f_1 g_1 + f_2 g_0 \\ r_3 &= f_0 g_3 + f_1 g_2 + f_2 g_1 + f_3 g_0 \\ r_4 &= f_1 g_3 + f_2 g_2 + f_3 g_1 \\ r_5 &= f_2 g_3 + f_3 g_2 \\ r_6 &= f_3 g_3 \end{split}$$

- ► Can easily load  $(f_0, f_1, f_2, f_3)$  and  $(g_0, g_1, g_2, g_3)$

- ▶ Multiply, obtain  $(f_0g_0, f_1g_1, f_2g_2, f_3g_3)$

- ▶ And now what?

#### Data shuffeling

$$r_0 = f_0 g_0$$

$$r_1 = f_0 g_1 + f_1 g_0$$

$$r_2 = f_0 g_2 + f_1 g_1 + f_2 g_0$$

$$r_3 = f_0 g_3 + f_1 g_2 + f_2 g_1 + f_3 g_0$$

$$r_4 = f_1 g_3 + f_2 g_2 + f_3 g_1$$

$$r_5 = f_2 g_3 + f_3 g_2$$

$$r_6 = f_3 g_3$$

- ► Can easily load  $(f_0, f_1, f_2, f_3)$  and  $(g_0, g_1, g_2, g_3)$

- Multiply, obtain  $(f_0g_0, f_1g_1, f_2g_2, f_3g_3)$

- And now what?

- Answer: Need to shuffle data in input and output registers

- Significant overhead, not clear that vectorization speeds up computation!

#### Efficient vectorization

- ▶ Most important question: Where does the parallelism come from?

- ► Easiest answer: Consider multiple batched encryptions, decryptions, signature computations, verifications, etc.

#### Efficient vectorization

- ▶ Most important question: Where does the parallelism come from?

- ► Easiest answer: Consider multiple batched encryptions, decryptions, signature computations, verifications, etc.

- ▶ Often: Can exploit lower-level parallelism

#### Efficient vectorization

- ▶ Most important question: Where does the parallelism come from?

- ► Easiest answer: Consider multiple batched encryptions, decryptions, signature computations, verifications, etc.

- ▶ Often: Can exploit lower-level parallelism

- ▶ Rule of thumb: parallelize on an as high as possible level

- ► Vectorization is hard to do as "add-on" optimization

- ▶ Reconsider algorithms, synergie with constant-time algorithms

- ► So far: considered vectors of integers

- ▶ How about arithmetic in binary fields?

- ► So far: considered vectors of integers

- ► How about arithmetic in binary fields?

- $\blacktriangleright$  Think of an n-bit register as a vector register with n 1-bit entries

- ▶ Operations are now bitwise XOR, AND, OR, etc.

- ► So far: considered vectors of integers

- ► How about arithmetic in binary fields?

- $\blacktriangleright$  Think of an n-bit register as a vector register with n 1-bit entries

- Operations are now bitwise XOR, AND, OR, etc.

- ► This is called bitslicing, introduced by Biham in 1997 for DES

- ► So far: considered vectors of integers

- ► How about arithmetic in binary fields?

- ▶ Think of an *n*-bit register as a vector register with *n* 1-bit entries

- Operations are now bitwise XOR, AND, OR, etc.

- ► This is called *bitslicing*, introduced by Biham in 1997 for DES

- ▶ Other views on bitslicing:

- Simulation of hardware implementations in software

# Going binary

- ► So far: considered vectors of integers

- ► How about arithmetic in binary fields?

- ightharpoonup Think of an n-bit register as a vector register with n 1-bit entries

- Operations are now bitwise XOR, AND, OR, etc.

- ► This is called *bitslicing*, introduced by Biham in 1997 for DES

- ▶ Other views on bitslicing:

- Simulation of hardware implementations in software

- Computations on a transposition of data

## Bitslicing issues

- ➤ XOR, AND, OR, etc are usually fast (e.g., 3 128-bit operations per cycle on Intel Core 2)

- Can be very fast for operations that are not natively supported (like arithmetic in binary fields)

## Bitslicing issues

- ➤ XOR, AND, OR, etc are usually fast (e.g., 3 128-bit operations per cycle on Intel Core 2)

- Can be very fast for operations that are not natively supported (like arithmetic in binary fields)

- ► Active data set increases massively (e.g., 128×)

- ► For "normal" vector operations, register space is increased accordingly (e.g, 16 256-bit vector registers vs. 16 64-bit integer registers)

- ▶ For bitslicing: Need to fit more data into the same registers

- Typical consequence: more loads and stores (that easily become the performance bottleneck)

- Vector instruction set introduced by Intel with Sandy Bridge and Ivy Bridge

- ▶ 256-bit vector registers YMM0,...,YMM15

- ▶ Overlap with 128-bit XMM registers

- Vector instruction set introduced by Intel with Sandy Bridge and Ivy Bridge

- ▶ 256-bit vector registers YMM0,...,YMM15

- ▶ Overlap with 128-bit XMM registers

- Instruction set only supports floating-point vector instructions on YMM registers

- Vector instruction set introduced by Intel with Sandy Bridge and Ivy Bridge

- ▶ 256-bit vector registers YMMO,...,YMM15

- ▶ Overlap with 128-bit XMM registers

- Instruction set only supports floating-point vector instructions on YMM registers

- ▶ Integer-vector instructions follow with AVX2 (Haswell)

- Vector instruction set introduced by Intel with Sandy Bridge and Ivy Bridge

- ▶ 256-bit vector registers YMMO,...,YMM15

- ▶ Overlap with 128-bit XMM registers

- Instruction set only supports floating-point vector instructions on YMM registers

- ▶ Integer-vector instructions follow with AVX2 (Haswell)

- Very powerful arithmetic: 1 double-precision vector multiplication and 1 double-precision vector addition per cycle (8 FLOPs per cycle per core)

- Vector instruction set introduced by Intel with Sandy Bridge and Ivy Bridge

- ▶ 256-bit vector registers YMMO,...,YMM15

- ▶ Overlap with 128-bit XMM registers

- Instruction set only supports floating-point vector instructions on YMM registers

- ▶ Integer-vector instructions follow with AVX2 (Haswell)

- ▶ Very powerful arithmetic: 1 double-precision vector multiplication and 1 double-precision vector addition per cycle (8 FLOPs per cycle per core)

- ▶ Also supported: XOR, AND, OR on YMM registers (1 per cycle)

- Vector instruction set introduced by Intel with Sandy Bridge and Ivy Bridge

- ▶ 256-bit vector registers YMMO,...,YMM15

- ▶ Overlap with 128-bit XMM registers

- Instruction set only supports floating-point vector instructions on YMM registers

- ▶ Integer-vector instructions follow with AVX2 (Haswell)

- ▶ Very powerful arithmetic: 1 double-precision vector multiplication and 1 double-precision vector addition per cycle (8 FLOPs per cycle per core)

- ▶ Also supported: XOR, AND, OR on YMM registers (1 per cycle)

- ► Alternative: XOR, AND, OR on XMM registers (3 per cycle)

- Vector instruction set introduced by Intel with Sandy Bridge and Ivy Bridge

- ▶ 256-bit vector registers YMMO,...,YMM15

- ▶ Overlap with 128-bit XMM registers

- Instruction set only supports floating-point vector instructions on YMM registers

- ▶ Integer-vector instructions follow with AVX2 (Haswell)

- ▶ Very powerful arithmetic: 1 double-precision vector multiplication and 1 double-precision vector addition per cycle (8 FLOPs per cycle per core)

- ▶ Also supported: XOR, AND, OR on YMM registers (1 per cycle)

- ▶ Alternative: XOR, AND, OR on XMM registers (3 per cycle)

- ► However, don't mix XMM and YMM instruction (context-switch penalty)

# Part II

Fast Lattice-Based Signatures

joint work with Tim Güneysu, Tobias Oder, and Thomas Pöppelmann

- ► Consider lattice-based signature scheme proposed by Güneysu, Lyubashevsky, and Pöppelmann at CHES 2012

- "Aggressively optimized" version of scheme by Lyubashevsky (Eurocrypt 2012)

- ► Consider lattice-based signature scheme proposed by Güneysu, Lyubashevsky, and Pöppelmann at CHES 2012

- "Aggressively optimized" version of scheme by Lyubashevsky (Eurocrypt 2012)

- ▶ Security level with the implemented parameters:

- original estimate: 100 bits (against traditional computers)

- ► Consider lattice-based signature scheme proposed by Güneysu, Lyubashevsky, and Pöppelmann at CHES 2012

- "Aggressively optimized" version of scheme by Lyubashevsky (Eurocrypt 2012)

- ▶ Security level with the implemented parameters:

- original estimate: 100 bits (against traditional computers)

- ▶ Lyubashevsky in 2013: 80 bits

- Consider lattice-based signature scheme proposed by Güneysu, Lyubashevsky, and Pöppelmann at CHES 2012

- "Aggressively optimized" version of scheme by Lyubashevsky (Eurocrypt 2012)

- ▶ Security level with the implemented parameters:

- original estimate: 100 bits (against traditional computers)

- ▶ Lyubashevsky in 2013: 80 bits

- ▶ 2014: ...?

- Consider lattice-based signature scheme proposed by Güneysu, Lyubashevsky, and Pöppelmann at CHES 2012

- "Aggressively optimized" version of scheme by Lyubashevsky (Eurocrypt 2012)

- ▶ Security level with the implemented parameters:

- original estimate: 100 bits (against traditional computers)

- ▶ Lyubashevsky in 2013: 80 bits

- **2014**: ...?

- ▶ This is not a mature, well understood cryptosystem

- Don't use it in applications, but study it!

- Consider lattice-based signature scheme proposed by Güneysu, Lyubashevsky, and Pöppelmann at CHES 2012

- "Aggressively optimized" version of scheme by Lyubashevsky (Eurocrypt 2012)

- ▶ Security level with the implemented parameters:

- original estimate: 100 bits (against traditional computers)

- ▶ Lyubashevsky in 2013: 80 bits

- **2014**: ...?

- ▶ This is not a mature, well understood cryptosystem

- Don't use it in applications, but study it!

- ▶ Implementation techniques are applicable more generally

#### Notation

- ightharpoonup n is a power of 2

- ightharpoonup p is a prime congruent to 1 modulo 2n (necessary for efficiency)

- $ightharpoonup \mathcal{R}$  is the ring  $\mathbb{F}_p[x]/\langle x^n+1\rangle$

- $ightharpoonup \mathcal{R}_k$  subset of  $\mathcal{R}$  with coefficients in [-k,k].

### Lattice hardness assumptions

#### Standard lattice hardness assumption

#### **Decisional Ring-LWE:**

Given  $(a_1, t_1), ..., (a_m, t_m) \in \mathcal{R} \times \mathcal{R}$ . Decide whether

- ▶  $t_i = a_i s + e_i$  where  $s, e_1, ..., e_m \leftarrow D_\sigma$  and  $a_i \stackrel{\$}{\leftarrow} \mathcal{R}$  ( $D_\sigma$  denotes a Gaussian distribution), or

- $(a_i, t_i)$  uniformly random from  $\mathcal{R} \times \mathcal{R}$ .

### Lattice hardness assumptions

#### Standard lattice hardness assumption

#### **Decisional Ring-LWE:**

Given  $(a_1, t_1), ..., (a_m, t_m) \in \mathcal{R} \times \mathcal{R}$ . Decide whether

- ▶  $t_i = a_i s + e_i$  where  $s, e_1, ..., e_m \leftarrow D_\sigma$  and  $a_i \stackrel{\$}{\leftarrow} \mathcal{R}$  ( $D_\sigma$  denotes a Gaussian distribution), or

- $(a_i, t_i)$  uniformly random from  $\mathcal{R} \times \mathcal{R}$ .

#### More "aggressive" hardness assumption

#### Decisional Compact Knapsack Problem (DCKP):

Given  $(a, t) \in \mathcal{R} \times \mathcal{R}$ .

- ▶ Decide whether  $t = as_1 + s_2$  where  $s_1, s_2 \stackrel{\$}{\leftarrow} \mathcal{R}_1$  and  $a \stackrel{\$}{\leftarrow} \mathcal{R}$ , or

- (a,t) uniformly random from  $\mathcal{R} \times \mathcal{R}$ .

# System parameters

#### **Parameters**

- $n = 2^{\ell_1}$

- ▶ Prime p with 2n|(p-1)

- $k = 2^{\ell_2}$  with  $\sqrt{p} < k \ll p$

- "Random"  $a \in \mathcal{R}$

- ► Hash function *H* to elements of R<sub>1</sub> with at most 32 non-zero coefficients

#### Example

- n = 512

- p = 8383489 (23 bits)

- $k = 2^{14}$

- ▶ Fixed random a

- ▶ ... more later

## Key generation

#### Secret key

•  $s_1, s_2$  sampled uniformly at random from  $\mathcal{R}_1$

#### Public key

$$t = as_1 + s_2$$

# Signing (simplified)

Compute a signature  $\sigma$  on a message M as follows:

- 1. Generate  $y_1,y_2$  uniformly at random from  $\mathcal{R}_k$

- 2. Compute  $c = H(ay_1 + y_2, M)$

- 3. Compute  $z_1 = s_1c + y_1$  and  $z_2 = s_2c + y_2$

- **4**. If  $z_1$  or  $z_2 \notin \mathcal{R}_{k-32}$ , goto step 1

- 5. Return  $\sigma = (z_1, z_2, c)$

# Verification (simplified)

Check signature  $\sigma = (z_1, z_2, c)$  on M as follows:

- 1. If  $z_1$  or  $z_2 \notin \mathcal{R}_{k-32}$ , reject

- 2. Else if  $c \neq H(az_1 + z_2 tc, M)$ , reject

- 3. Else accept

# Verification (simplified)

Check signature  $\sigma = (z_1, z_2, c)$  on M as follows:

- 1. If  $z_1$  or  $z_2 \notin \mathcal{R}_{k-32}$ , reject

- 2. Else if  $c \neq H(az_1 + z_2 tc, M)$ , reject

- 3. Else accept

#### Correctness

$$az_1 + z_2 - tc$$

$$= a(s_1c + y_1) + (s_2c + y_2) - (as_1 + s_2)c$$

$$= as_1c + ay_1 + s_2c + y_2 - as_1c - s_2c$$

$$= ay_1 + y_2$$

# Software implementation, first considerations

#### Key generation

- ▶ Main operation: sampling random coefficients in  $\{-1,0,1\}$

- ▶ One multiplication of fixed a by  $s_1$

# Software implementation, first considerations

#### Key generation

- ▶ Main operation: sampling random coefficients in  $\{-1,0,1\}$

- lacktriangle One multiplication of fixed a by  $s_1$

#### Signing

- Expected number of signing attempts: 7

- ► Each attempt:

- ▶ Sample  $y_1, y_2$  uniformly at random from  $\mathcal{R}_k$

- ▶ Two sparse multiplications  $s_1c$  and  $s_2c$

- ▶ One multiplication  $ay_1$  by constant a

# Software implementation, first considerations

#### Key generation

- ▶ Main operation: sampling random coefficients in  $\{-1,0,1\}$

- ▶ One multiplication of fixed a by  $s_1$

#### Signing

- Expected number of signing attempts: 7

- ► Each attempt:

- ▶ Sample  $y_1, y_2$  uniformly at random from  $\mathcal{R}_k$

- ▶ Two sparse multiplications  $s_1c$  and  $s_2c$

- ▶ One multiplication  $ay_1$  by constant a

#### Verification

- ▶ One sparse multiplication ct

- ightharpoonup One multiplication  $az_1$  by constant a

#### The function H

Need to hash an arbitrary string S to an element  $c=(c_0+c_1x+\cdots+c_{511}x^{511})$  of  $\mathcal{R}_1$  with at most 32 non-zero entries

#### The function H

Need to hash an arbitrary string S to an element  $c=(c_0+c_1x+\cdots+c_{511}x^{511})$  of  $\mathcal{R}_1$  with at most 32 non-zero entries

- ▶ First apply SHA-256, truncate to 160-bit hash h

- ▶ Map h injectively to c as follows:

- ▶ Split  $(h_0, \ldots, h_{31})$ , each  $h_i$  with 5 bits

- Split each  $h_i$  into  $(h_{i0}, h_{it})$ , where  $h_{i0}$  is one bit and  $h_{it}$  is a 4-bit integer

- ▶  $h_{it}$  indicates which of the 16 coefficients  $c_{16i}, \ldots, c_{16i+15}$  is nonzero

- ▶ If  $h_{i0} = 0$  set this coefficient to -1 else to 1

- ▶ How do we get an integer, uniformly at random from [0, m-1]?

- ▶ Let's say that m-1 has  $\ell$  bits

- ▶ Let's say that we can get random bits (e.g., from /dev/urandom)

- ▶ How do we get an integer, uniformly at random from [0, m-1]?

- ▶ Let's say that m-1 has  $\ell$  bits

- ▶ Let's say that we can get random bits (e.g., from /dev/urandom)

- ► Two answers:

- 1. Obtain a random  $\ell$ -bit integer, reject until it is in [0,m-1]

- ▶ How do we get an integer, uniformly at random from [0, m-1]?

- ▶ Let's say that m-1 has  $\ell$  bits

- ▶ Let's say that we can get random bits (e.g., from /dev/urandom)

- ► Two answers:

- 1. Obtain a random  $\ell$ -bit integer, reject until it is in [0, m-1]

- 2. Obtain a much larger integer, reduce mod m (close to uniform)

- ▶ How do we get an integer, uniformly at random from [0, m-1]?

- ▶ Let's say that m-1 has  $\ell$  bits

- ▶ Let's say that we can get random bits (e.g., from /dev/urandom)

- ► Two answers:

- 1. Obtain a random  $\ell$ -bit integer, reject until it is in [0, m-1]

- 2. Obtain a much larger integer, reduce mod m (close to uniform)

- ▶ Probability of rejection in 1. depends on m, it's between 0 and 1/2

- ▶ How do we get an integer, uniformly at random from [0, m-1]?

- ▶ Let's say that m-1 has  $\ell$  bits

- ▶ Let's say that we can get random bits (e.g., from /dev/urandom)

- ► Two answers:

- 1. Obtain a random  $\ell$ -bit integer, reject until it is in [0, m-1]

- 2. Obtain a much larger integer, reduce mod m (close to uniform)

- ▶ Probability of rejection in 1. depends on m, it's between 0 and 1/2

- ▶ Problem with both 1. and 2.: /dev/urandom is slow

### Faster random sampling

- Only read seed from /dev/urandom, use fast Salsa20 stream cipher

- lacktriangle Salsa20 fast only for long streams, 3 bytes cost as much as 64

### Faster random sampling

- Only read seed from /dev/urandom, use fast Salsa20 stream cipher

- $\triangleright$  Salsa20 fast only for long streams, 3 bytes cost as much as 64

- ▶ We want truly uniform distribution from [-k, k], recall that  $k = 2^{14}$

- ▶ We want only one call to Salsa20

### Faster random sampling

- Only read seed from /dev/urandom, use fast Salsa20 stream cipher

- ▶ Salsa20 fast only for long streams, 3 bytes cost as much as 64

- ▶ We want truly uniform distribution from [-k, k], recall that  $k = 2^{14}$

- ▶ We want only one call to Salsa20

- ▶ Combine approaches 1 and 2 as follows:

- 1. Obtain  $4 \cdot (528)$  random bytes from Salsa20

- 2. Interpret these bytes as 528 32-bit integers

- 3. Discard integers  $\geq (2k+1) \cdot \lfloor 2^{32}/(2k+1) \rfloor$ .

- 4. Probability to discard an integer:  $2^{-30}$

- 5. We have 16 additional integers, replace discarded integers by those

- 6. If more than 16 integers are discarded, restart with step 1

- 7. For each integer r compute  $r \mod (2k+1) k$

### Faster random sampling

- Only read seed from /dev/urandom, use fast Salsa20 stream cipher

- $\triangleright$  Salsa20 fast only for long streams, 3 bytes cost as much as 64

- ▶ We want truly uniform distribution from [-k, k], recall that  $k = 2^{14}$

- ▶ We want only one call to Salsa20

- ▶ Combine approaches 1 and 2 as follows:

- 1. Obtain  $4 \cdot (528)$  random bytes from Salsa20

- 2. Interpret these bytes as 528 32-bit integers

- 3. Discard integers  $\geq (2k+1) \cdot \lfloor 2^{32}/(2k+1) \rfloor$ .

- 4. Probability to discard an integer:  $2^{-30}$

- 5. We have 16 additional integers, replace discarded integers by those

- 6. If more than 16 integers are discarded, restart with step 1

- 7. For each integer r compute  $r \mod (2k+1) k$

- ▶ Similar approach to sample coefficients in  $\{-1, 0, 1\}$

- ▶ Only difference: Use bytes instead of 32-bit integers

```

typedef double __attribute__ ((aligned (32))) r_elem[512];

```

ightharpoonup represent  $a=\sum_{i=0}^{511}a_iX^i$  as  $(a_0,\ldots,a_{511})$ :

```

\label{eq:typedef} \mbox{ double $\_$-attribute}\_ \mbox{ ((aligned (32))) $r_elem[512]$;}

```

Use AVX double-precision instructions for addition and multiplication of coefficients

```

typedef double __attribute__ ((aligned (32))) r_elem[512];

```

- Use AVX double-precision instructions for addition and multiplication of coefficients

- ▶ Modular reduction of a coefficient a:

- ▶ Precompute double-precision approximation  $\overline{p^{-1}}$  of  $p^{-1}$

```

typedef double __attribute__ ((aligned (32))) r_elem[512];

```

- Use AVX double-precision instructions for addition and multiplication of coefficients

- ▶ Modular reduction of a coefficient a:

- lacktriangle Precompute double-precision approximation  $\overline{p^{-1}}$  of  $p^{-1}$

- ▶ Compute  $c \leftarrow a \cdot \overline{p^{-1}}$

- Round c (high-throughput vroundpd instruction)

- ▶ Compute  $c \leftarrow c \cdot p$

- ▶ Subtract c from a

```

typedef double __attribute__ ((aligned (32))) r_elem[512];

```

- Use AVX double-precision instructions for addition and multiplication of coefficients

- ▶ Modular reduction of a coefficient a:

- lacktriangle Precompute double-precision approximation  $\overline{p^{-1}}$  of  $p^{-1}$

- ▶ Compute  $c \leftarrow a \cdot \overline{p^{-1}}$

- Round c (high-throughput vroundpd instruction)

- ▶ Compute  $c \leftarrow c \cdot p$

- ▶ Subtract c from a

- $\blacktriangleright$  Rounding mode determines whether this maps to  $[-\frac{p-1}{2},\frac{p-1}{2}]$  or to [0,p-1]

```

typedef double __attribute__ ((aligned (32))) r_elem[512];

```

- Use AVX double-precision instructions for addition and multiplication of coefficients

- ▶ Modular reduction of a coefficient a:

- lacktriangle Precompute double-precision approximation  $\overline{p^{-1}}$  of  $p^{-1}$

- ▶ Compute  $c \leftarrow a \cdot \overline{p^{-1}}$

- lacktriangle Round c (high-throughput vroundpd instruction)

- ▶ Compute  $c \leftarrow c \cdot p$

- ▶ Subtract c from a

- Properties Rounding mode determines whether this maps to  $[-\frac{p-1}{2},\frac{p-1}{2}]$  or to [0,p-1]

- ▶ Use lazy reduction: product of two 22-bit numbers has 44 bits, quite some space in the 53-bit mantissa

- ▶ Let  $\omega$  be a 512th root of unity in  $\mathbb{F}_p$  and  $\psi^2 = \omega$

- ▶ The number-theoretic transform NTT $_{\omega}$  of  $a=(a_0,\ldots,a_{511})$  is defined as

$$\mathsf{NTT}_{\omega}(a) = (A_0,\ldots,A_{511}) ext{ with } A_i = \sum_{j=0}^{511} a_j \omega^{ij}$$

- ▶ Let  $\omega$  be a 512th root of unity in  $\mathbb{F}_p$  and  $\psi^2 = \omega$

- ▶ The number-theoretic transform NTT $_{\omega}$  of  $a=(a_0,\ldots,a_{511})$  is defined as

$$\mathsf{NTT}_{\omega}(a) = (A_0,\ldots,A_{511}) ext{ with } A_i = \sum_{j=0}^{511} a_j \omega^{ij}$$

- ▶ Consider multiplication  $d = a \cdot b$  in  $\mathcal{R}$

- Compute

$$ar{a}=(a_0,\psi a_1,\dots,\psi^{511}a_{511})$$

and  $ar{b}=(b_0,\psi b_1,\dots,\psi^{511}b_{511})$

- ▶ Let  $\omega$  be a 512th root of unity in  $\mathbb{F}_p$  and  $\psi^2 = \omega$

- ▶ The number-theoretic transform NTT $_{\omega}$  of  $a=(a_0,\ldots,a_{511})$  is defined as

$$\mathsf{NTT}_\omega(a) = (A_0,\ldots,A_{511}) ext{ with } A_i = \sum_{j=0}^{511} a_j \omega^{ij}$$

- ▶ Consider multiplication  $d = a \cdot b$  in  $\mathcal{R}$

- Compute

$$\bar{a}=(a_0,\psi a_1,\dots,\psi^{511}a_{511}) \text{ and } \\ \bar{b}=(b_0,\psi b_1,\dots,\psi^{511}b_{511})$$

• Obtain  $\bar{d} = (d_0, \psi d_1, \dots, \psi^{511} d_{511})$  as

$$\bar{d} = \mathsf{NTT}_{\omega}^{-1}(\mathsf{NTT}_{\omega}(\bar{a}) \circ \mathsf{NTT}_{\omega}(\bar{b})),$$

where o denotes component-wise multiplication

- ▶ Let  $\omega$  be a 512th root of unity in  $\mathbb{F}_p$  and  $\psi^2 = \omega$

- ▶ The number-theoretic transform NTT $_{\omega}$  of  $a=(a_0,\ldots,a_{511})$  is defined as

$$\mathsf{NTT}_\omega(a) = (A_0,\ldots,A_{511}) ext{ with } A_i = \sum_{j=0}^{511} a_j \omega^{ij}$$

- Consider multiplication  $d = a \cdot b$  in  $\mathcal R$

- Compute

$$ar{a}=(a_0,\psi a_1,\dots,\psi^{511}a_{511})$$

and  $ar{b}=(b_0,\psi b_1,\dots,\psi^{511}b_{511})$

• Obtain  $\bar{d} = (d_0, \psi d_1, \dots, \psi^{511} d_{511})$  as

$$\bar{d} = \mathsf{NTT}_{\omega}^{-1}(\mathsf{NTT}_{\omega}(\bar{a}) \circ \mathsf{NTT}_{\omega}(\bar{b})),$$

where o denotes component-wise multiplication

Component-wise multiplication is trivially vectorizable

- ▶ FFT in a finite field

- ▶ Evaluate polynomial  $f = a_0 + a_1x + \cdots + a_{n-1}x^{n-1}$  at all n-th roots of unity

- ► Divide-and-conquer approach

- Write polynomial f as  $f_0(x^2) + x f_1(x^2)$

- FFT in a finite field

- ▶ Evaluate polynomial  $f = a_0 + a_1x + \cdots + a_{n-1}x^{n-1}$  at all n-th roots of unity

- Divide-and-conquer approach

- Write polynomial f as  $f_0(x^2) + x f_1(x^2)$

- Huge overlap between evaluating

$$f(\beta) = f_0(\beta^2) + \beta f_1(\beta^2) \text{ and}$$

$$f(-\beta) = f_0(\beta^2) - \beta f_1(\beta^2)$$

- FFT in a finite field

- Evaluate polynomial  $f = a_0 + a_1 x + \cdots + a_{n-1} x^{n-1}$  at all n-th roots of unity

- ► Divide-and-conquer approach

- Write polynomial f as  $f_0(x^2) + x f_1(x^2)$

- Huge overlap between evaluating

$$f(\beta) = f_0(\beta^2) + \beta f_1(\beta^2) \text{ and}$$

$$f(-\beta) = f_0(\beta^2) - \beta f_1(\beta^2)$$

- $f_0$  has n/2 coefficients

- ightharpoonup Evaluate  $f_0$  at all (n/2)-th roots of unity by recursive application

- ▶ FFT in a finite field

- Evaluate polynomial  $f = a_0 + a_1 x + \cdots + a_{n-1} x^{n-1}$  at all n-th roots of unity

- ► Divide-and-conquer approach

- Write polynomial f as  $f_0(x^2) + x f_1(x^2)$

- Huge overlap between evaluating

$$f(\beta) = f_0(\beta^2) + \beta f_1(\beta^2) \text{ and}$$

$$f(-\beta) = f_0(\beta^2) - \beta f_1(\beta^2)$$

- $f_0$  has n/2 coefficients

- ightharpoonup Evaluate  $f_0$  at all (n/2)-th roots of unity by recursive application

- ▶ Same for  $f_1$

- ▶ FFT in a finite field

- Evaluate polynomial  $f = a_0 + a_1 x + \cdots + a_{n-1} x^{n-1}$  at all n-th roots of unity

- Divide-and-conquer approach

- Write polynomial f as  $f_0(x^2) + x f_1(x^2)$

- Huge overlap between evaluating

$$f(\beta) = f_0(\beta^2) + \beta f_1(\beta^2) \text{ and}$$

$$f(-\beta) = f_0(\beta^2) - \beta f_1(\beta^2)$$

- $f_0$  has n/2 coefficients

- ▶ Evaluate  $f_0$  at all (n/2)-th roots of unity by recursive application

- $\triangleright$  Same for  $f_1$

- For n = 512 we have 9 levels of recursion

- First thing to do: replace recursion by iteration

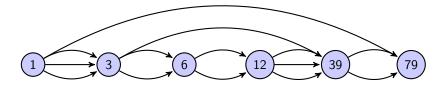

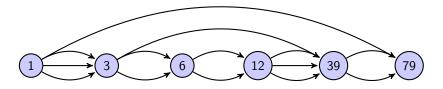

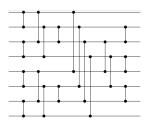

- ▶ Loop over 9 levels with 256 "butterfly transformations" each

- ▶ Butterfly on level *k*:

- lacktriangle Pick up  $a_i$  and  $a_{i+2^k}$

- Multiply  $a_{i+2^k}$  by a power of  $\omega$  to obtain t

- ▶ Compute  $a_{i+2^k} \leftarrow a_i t$

- ▶ Compute  $a_i \leftarrow a_i + t$

- ▶ Easy vectorization on levels k = 2, ..., 8:

- Pick up  $v_0 = a_i, a_{i+1}, a_{i+2}, a_{i+3}$  and  $v_1 = a_{i+2k}, a_{i+2k+1}, a_{i+2k+2}, a_{i+2k+3}$

- ightharpoonup Perform all operations on  $v_0$  and  $v_1$

- Levels 0 and 1: More tricky: Use permutation instructions and "horizontal additions"

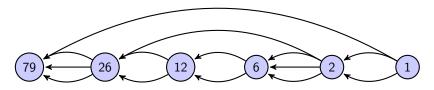

▶ Main bottleneck of NTT: memory access

- ▶ Main bottleneck of NTT: memory access

- On one level of butterfly, pairs of values interact

- ► Through two levels, 4-tuples interact

- ► Through three levels, 8-tuples interact, etc.

- ▶ Main bottleneck of NTT: memory access

- On one level of butterfly, pairs of values interact

- ► Through two levels, 4-tuples interact

- ► Through three levels, 8-tuples interact, etc.

- ▶ Merge 3 levels: Load  $8 \cdot 4 = 32$  values, perform arithmetic, store the results

- ▶ Main bottleneck of NTT: memory access

- On one level of butterfly, pairs of values interact

- ► Through two levels, 4-tuples interact

- ► Through three levels, 8-tuples interact, etc.

- ▶ Merge 3 levels: Load  $8 \cdot 4 = 32$  values, perform arithmetic, store the results

- ▶ Final performance for NTT: 4484 cycles on Ivy Bridge

- ▶ Performance for multiplication in  $\mathcal{R}$ : 16096 cycles

- ▶ Multiplication by constant *a*: 11044 cycles

#### Results

- ▶ Keypair generation: 31140 cycles on Intel Ivy Bridge

- ▶ Signing: 634988 cycles on average

- ▶ Verification: 45036 cycles

### Results

▶ Keypair generation: 31140 cycles on Intel Ivy Bridge

▶ Signing: 634988 cycles on average

▶ Verification: 45036 cycles

▶ Public key: 1536 bytes

▶ Secret key: 256 bytes

► Signature: 1184 bytes

# Comparison

| Software                 | Cycles  |          | Sizes |        |

|--------------------------|---------|----------|-------|--------|

| Our work                 | sign:   | 634988   | pk:   | 1536   |

|                          | verify: | 45036    | sk:   | 256    |

|                          |         |          | sig:  | 1184   |

| mqqsig160                | sign:   | 1996     | pk:   | 206112 |

|                          | verify: | 33220    | sk:   | 401    |

|                          |         |          | sig:  | 20     |

| rainbow5640              | sign:   | 53872    | pk:   | 44160  |

|                          | verify: | 34808    | sk:   | 86240  |

|                          |         |          | sig:  | 37     |

| pflash1                  | sign:   | 1473364  | pk:   | 72124  |

|                          | verify: | 286168   | sk:   | 5550   |

|                          |         |          | sig:  | 37     |

| tts6440                  | sign:   | 33728    | pk:   | 57600  |

|                          | verify: | 49248    | sk:   | 16608  |

|                          |         |          | sig:  | 43     |

| XMSS                     | sign:   | 7261100* | pk:   | 912    |

| (H = 20, w = 4, AES-128) | verify: | 556600*  | sk:   | 19     |

|                          |         |          | sig:  | 2451   |

#### References

► Tim Güneysu, Tobias Oder, Thomas Pöppelmann, and Peter Schwabe. Software speed records for lattice-based signatures., PQCrypto 2013.

http://cryptojedi.org/papers/#lattisigns

► Software is online (public domain) at http://cryptojedi.org/crypto/#lattisigns

# Part III

McBits: Fast code-based cryptography

joint work with Daniel J. Bernstein and Tung Chou

## Public-key authenticated encryption

lacktriangle Alice generates a key pair (sk, pk), publishes pk, keeps sk secret

### Public-key authenticated encryption

- lacktriangle Alice generates a key pair (sk, pk), publishes pk, keeps sk secret

- ▶ Bob takes some message *M* and *pk* and computes **authenticated ciphertext** *C*, sends *C* to Alice

### Public-key authenticated encryption

- lacktriangle Alice generates a key pair (sk, pk), publishes pk, keeps sk secret

- ▶ Bob takes some message M and pk and computes **authenticated ciphertext** C, sends C to Alice

- $\blacktriangleright$  Alice uses sk to check authenticity of C and decrypt

#### **Parameters**

- ▶ Integers m, q, n, t, k, such that

- $n < q = 2^m$

- k = n mt

- $t \ge 2$

$$m = 12,

n = q = 4096

k = 3604

t = 41$$

#### **Parameters**

- ▶ Integers m, q, n, t, k, such that

- $n < q = 2^m$

- k = n mt

- t > 2

- lacktriangle An s-bit-key stream cipher S

- m = 12,n = q = 4096k = 3604t = 41

- ightharpoonup S = Salsa20 (s = 256)

#### **Parameters**

- ▶ Integers m, q, n, t, k, such that

- $n < q = 2^m$

- k = n mt

- ▶ t > 2

- $\blacktriangleright$  An s-bit-key stream cipher S

- An a-bit-key authenticator (MAC) A

- m = 12,n = q = 4096k = 3604t = 41

- ightharpoonup S = Salsa20 (s = 256)

- $A = \text{Poly1305} \ (a = 256)$

#### **Parameters**

- ▶ Integers m, q, n, t, k, such that

- $n < q = 2^m$

- k = n mt

- ▶ t > 2

- ► An s-bit-key stream cipher S

- An a-bit-key authenticator (MAC) A

- ► An (s + a)-bit-output hash function H

- m = 12,n = q = 4096k = 3604t = 41

- ightharpoonup S = Salsa20 (s = 256)

- A = Poly1305 (a = 256)

- ► *H* = SHA-512

### Key generation

### Secret key

- lacktriangle A random sequence  $(lpha_1,\ldots,lpha_n)$  of distinct elements in  $\mathbb{F}_q$

- $\blacktriangleright$  A irreducible degree-t polynomial  $g\in\mathbb{F}_q[x]$

- lacktriangle A random sequence  $(lpha_1,\ldots,lpha_n)$  of distinct elements in  $\mathbb{F}_q$

- $\blacktriangleright$  A irreducible degree-t polynomial  $g\in\mathbb{F}_q[x]$

- Compute the secret matrix

$$\begin{pmatrix} 1/g(\alpha_1) & 1/g(\alpha_2) & \cdots & 1/g(\alpha_n) \\ \alpha_1/g(\alpha_1) & \alpha_2/g(\alpha_2) & \cdots & \alpha_n/g(\alpha_n) \\ \vdots & \vdots & \ddots & \vdots \\ \alpha_1^{t-1}/g(\alpha_1) & \alpha_2^{t-1}/g(\alpha_2) & \cdots & \alpha_n^{t-1}/g(\alpha_n) \end{pmatrix} \in \mathbb{F}_q^{t \times n}$$

- lacktriangle A random sequence  $(lpha_1,\ldots,lpha_n)$  of distinct elements in  $\mathbb{F}_q$

- $\blacktriangleright$  A irreducible degree-t polynomial  $g\in\mathbb{F}_q[x]$

- Compute the secret matrix

$$\begin{pmatrix} 1/g(\alpha_1) & 1/g(\alpha_2) & \cdots & 1/g(\alpha_n) \\ \alpha_1/g(\alpha_1) & \alpha_2/g(\alpha_2) & \cdots & \alpha_n/g(\alpha_n) \\ \vdots & \vdots & \ddots & \vdots \\ \alpha_1^{t-1}/g(\alpha_1) & \alpha_2^{t-1}/g(\alpha_2) & \cdots & \alpha_n^{t-1}/g(\alpha_n) \end{pmatrix} \in \mathbb{F}_q^{t \times n}$$

- ▶ Replace all entries by a column of m bits in a standard basis of  $\mathbb{F}_q$  over  $\mathbb{F}_2$

- $lackbox{Obtain a matrix } H \in \mathbb{F}_2^{mt imes n}$

- lacktriangle A random sequence  $(lpha_1,\ldots,lpha_n)$  of distinct elements in  $\mathbb{F}_q$

- lacktriangle A irreducible degree-t polynomial  $g \in \mathbb{F}_q[x]$

- Compute the secret matrix

$$\begin{pmatrix} 1/g(\alpha_1) & 1/g(\alpha_2) & \cdots & 1/g(\alpha_n) \\ \alpha_1/g(\alpha_1) & \alpha_2/g(\alpha_2) & \cdots & \alpha_n/g(\alpha_n) \\ \vdots & \vdots & \ddots & \vdots \\ \alpha_1^{t-1}/g(\alpha_1) & \alpha_2^{t-1}/g(\alpha_2) & \cdots & \alpha_n^{t-1}/g(\alpha_n) \end{pmatrix} \in \mathbb{F}_q^{t \times n}$$

- ▶ Replace all entries by a column of m bits in a standard basis of  $\mathbb{F}_q$  over  $\mathbb{F}_2$

- $lackbox{Obtain a matrix } H \in \mathbb{F}_2^{mt imes n}$

- ▶ H is a *secret* parity-check matrix of the Goppa code  $\Gamma = \Gamma_2(\alpha_1, \dots, \alpha_n, g)$

- lacktriangle A random sequence  $(lpha_1,\ldots,lpha_n)$  of distinct elements in  $\mathbb{F}_q$

- lacktriangle A irreducible degree-t polynomial  $g \in \mathbb{F}_q[x]$

- Compute the secret matrix

$$\begin{pmatrix} 1/g(\alpha_1) & 1/g(\alpha_2) & \cdots & 1/g(\alpha_n) \\ \alpha_1/g(\alpha_1) & \alpha_2/g(\alpha_2) & \cdots & \alpha_n/g(\alpha_n) \\ \vdots & \vdots & \ddots & \vdots \\ \alpha_1^{t-1}/g(\alpha_1) & \alpha_2^{t-1}/g(\alpha_2) & \cdots & \alpha_n^{t-1}/g(\alpha_n) \end{pmatrix} \in \mathbb{F}_q^{t \times n}$$

- ▶ Replace all entries by a column of m bits in a standard basis of  $\mathbb{F}_q$  over  $\mathbb{F}_2$

- $lackbox{ Obtain a matrix } H \in \mathbb{F}_2^{mt imes n}$

- ightharpoonup H is a *secret* parity-check matrix of the Goppa code  $\Gamma = \Gamma_2(\alpha_1,\ldots,\alpha_n,g)$

- ▶ The secret key is  $(\alpha_1, \ldots, \alpha_n, g)$

### Public key

- $lackbox{ Perform Gaussian elimination on } H$  to obtain a matrix K whose left  $tm \times tm$  submatrix is the identity matrix

- ightharpoonup K is a *public* parity-check matrix for  $\Gamma$

- ► The public key is *K*

## Encryption

- $lackbox{ }$  Generate a random weight-t vector  $e \in \mathbb{F}_2^n$

- ightharpoonup Compute w=Ke

- ▶ Compute H(e) to obtain an (s+a)-bit string  $(k_{enc}, k_{auth})$

- $\blacktriangleright$  Encrypt the message M with the stream cipher S under key  $k_{enc}$  to obtain ciphertext C

- lacktriangle Compute authentication tag a on C using A with key  $k_{auth}$

- ▶ Send (a, w, C)

## Decryption

- ightharpoonup Receive (a, w, C)

- ightharpoonup Decode w to obtain weight-t string e

- ▶ Hash e with H to obtain  $(k_{enc}, k_{auth})$

- ▶ Verify that a is a valid authentication tag on C using A with  $k_{auth}$

- ▶ Use S with  $k_{enc}$  to decrypt and obtain M

# Software implementation, first considerations

### Key generation

- Key generation is not performance critical

- ▶ Some hassle to make constant-time, but possible

## Software implementation, first considerations

### Key generation

- Key generation is not performance critical

- ▶ Some hassle to make constant-time, but possible

### Encryption

- $lackbox{\ }$  Computation of Ke is simply XORing t columns of mt bits each

- ▶ In our example mt = 492, almost 512; great for fast vector XORs

- But: have to be careful to not leak information about e

- ▶ This talk: ignore implementation of *H*, *S*, and *A*

## Software implementation, first considerations

#### Key generation

- Key generation is not performance critical

- ▶ Some hassle to make constant-time, but possible

### Encryption

- lacktriangle Computation of Ke is simply XORing t columns of mt bits each

- ▶ In our example mt = 492, almost 512; great for fast vector XORs

- But: have to be careful to not leak information about e

- $\blacktriangleright$  This talk: ignore implementation of H, S, and A

### Decryption

- lacktriangle Decryption is mainly decoding, lots of operations  $\mathbb{F}_q$

- Decryption has to run in constant time!

- Obviously, decoding of w is the interesting part

▶ Start with some  $v \in \mathbb{F}_2^n$ , such that Kv = w

- ▶ Start with some  $v \in \mathbb{F}_2^n$ , such that Kv = w

- ▶ Compute a Goppa syndrome  $s_0, \ldots, s_{2t-1}$

- Use Berlekamp-Massey algorithm to obtain error-locator polynomial f of degree t

- ▶ Start with some  $v \in \mathbb{F}_2^n$ , such that Kv = w

- ▶ Compute a Goppa syndrome  $s_0, \ldots, s_{2t-1}$

- lackbox Use Berlekamp-Massey algorithm to obtain error-locator polynomial f of degree t

- ► Compute *t* roots of this polynomial

- For each root  $r_j = \alpha_i$ , set error bit at position i in e

- ▶ Start with some  $v \in \mathbb{F}_2^n$ , such that Kv = w

- ▶ Compute a Goppa syndrome  $s_0, \ldots, s_{2t-1}$

- Use Berlekamp-Massey algorithm to obtain error-locator polynomial f of degree t

- Compute t roots of this polynomial

- For each root  $r_j = \alpha_i$ , set error bit at position i in e

- lacktriangle All these computation work on medium-size polynomials over  $\mathbb{F}_q$