## MC722

## Organização de Computadores

2012 Prof. Paulo Cesar Centoducatte ducatte@ic.unicamp.br www.ic.unicamp.br/~ducatte

Sistemas de Memória

Definições

Cache

## MC722 Arquitetura de Computadores Sistemas de Memória "DDCA" - (Capítulo 8) "COD" - (Capítulo 7)

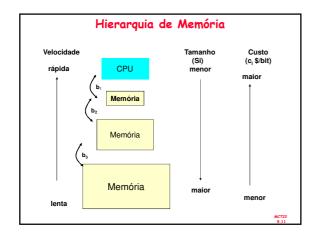

## Sumário Explorando Hierarquia de Memória - Hierarquia de Memória Custo e Velocidade Principio da Localidade » Localidade Temporal » Localidade Espacial Visão em Dois Níveis Direct Mapped Cache Via de Dados com Pipeline Tamanho da Cache em bits Tratamento de Cache Misses

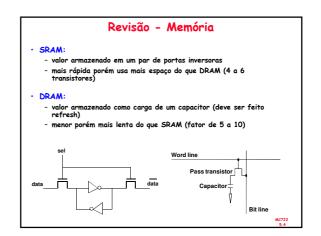

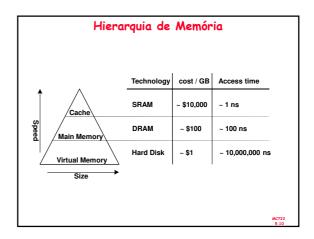

## Revisão · Usuários querem memórias grandes e rápidas - SRAM access times: 2 - 25ns; custo de \$100 a \$250 por Mbyte. - DRAM access times: 60-120ns; custo de \$5 a \$10 por Mbyte - Disk access times: 10 a 20 milhões de ns; custo de \$.10 a \$.20 por Mbyte.

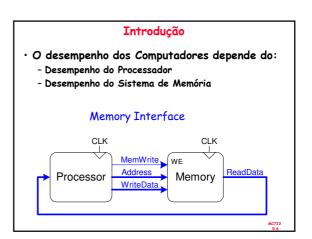

# Tintrodução Até agora consideramos que a memória pode ser acessada em 1 ciclo de clock Porém isso não é verdade desde a década de 80

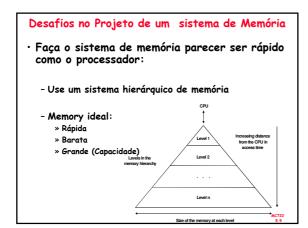

## Desafios no Projeto de um sistema de Memória

- · Memórias:

- SRAM access times: 2 25ns; custo de \$100 a \$250 por Mbyte.

- DRAM access times: 60-120ns; custo de \$5 a \$10 por Mbyte

- Disk access times: 10 a 20 milhões de ns; custo de \$.10 a \$.20 por Mbyte.

- · Usuários querem memórias grandes e rápidas

- · Usuários querem memórias grandes e baratas

WC722 5.8

## Hierarquia de Memória (Custo e Velocidade)

· Custo médio do sistema (\$/bit)

$$\frac{S_1 C_1 + S_2 2_3 + \dots + S_n C_n}{S_1 + S_2 + \dots + S_n}$$

- · Objetivos do sistema

- Custo médio ≈ custo do nível mais barato (disco)

- Velocidade do sistema ≈ velocidade do mais rápido (cache)

MC72

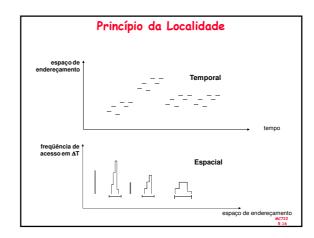

## Localidade

- Principio que torna possível o uso de hierarquia de memória

- Um programa acessa uma porção relativamente pequena do espaço endereçável em um instante de tempo qualquer.

- Localidade temporal: Se um item é referenciado, ele tende a ser referenciado novamente.

- Exemplo → loops ( instruções e dados).

- Localidade Espacial: Se um item é referenciado, itens cujos endereços são próximos a este, tendem a ser referenciados também.

- » Exemplo → acesso a dados de um array.

MC722 5.13

## Localidade - Definições

- Bloco → mínima unidade de informação que pode ou não estar presente em dois níveis de hierarquia de memória.

- Hit se o dado acessado aparece em algum bloco no nível superior.

- Miss → se o dado acessado não aparece em algum bloco do nível superior.

- Hit ratio (hit rate) > razão hits pelo número total de acessos ao nível superior.

- Miss ratio (miss rate) → razão de misses pelo número total de acessos ao nível superior → miss ratio = 1 - hit ratio.

- Hit time > tempo de acesso ao nível superior da hierarquia de memória, que inclui o tempo necessário para saber se no acesso ocorrerá um hit ou um miss.

- Miss penalty → tempo para recolocar um bloco no nível superior e enviá-lo ao processador, quando ocorre um miss. O maior componente do miss penalty é o tempo de acesso ao nível imediatamente inferior da hierarquia de memória.

MC722

## Localidade - Definições

- · Average memory access time (AMAT)

- tempo médio gasto para o processador fazer um acesso à memória

AMAT = HitTime + MissRate × MissPenalty

MC722 5.15

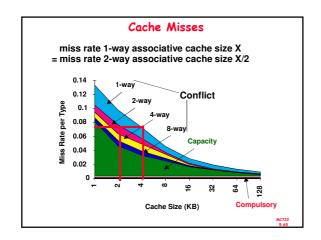

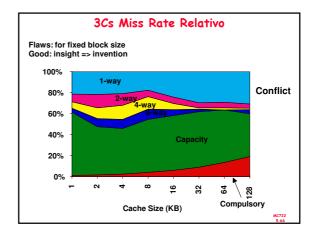

Miss Rate

## Desempenho de Memória

## Exemplo 1:

- · Um programa tem 2000 instruções de load e store

- · 1250 dos dados são encontrados na cache

- · O resto são encontrados em outro nível da hierarquia de memória

- · Qual é o miss e hit rates para a cache?

MC722

## Desempenho de Memória

## Exemplo 2:

- Suponha um processador com 2 níveis de hierarquia de memória: cache e memória principal

- $t_{\text{cache}} = 1$  ciclo,  $t_{MM} = 100$  ciclos

- · Qual é o AMAT do programa do exemplo anterior?

$AMAT = HitTime + MissRate \times MissPenalty$

AMAT =  $t_{cache} + MR_{cache}(t_{MM})$ = [1 + 0.375(100)] cycles = 38.5 cycles

> MC72 5.18

## Cache

"A safe place to hide things"

- · Melhora o tempo de acesso à memória

- · É rápida (usualmente ~ 1 ciclo de access time)

- · Mantém os dados usados mais recentemente

- · Questões no projeto de uma Cache :

- Qual o dado deve ser mantido na cache?

- Como localizar o dado?

- Qual dado trocar?

MC722

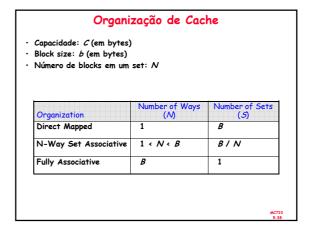

## Questões no Projeto de uma Cache

## Terminologia:

- Capacidade (C): número de bits (bytes) de dados que a cache armazena

- Número de sets (5): cada endereço de memória mapeia um set na cache

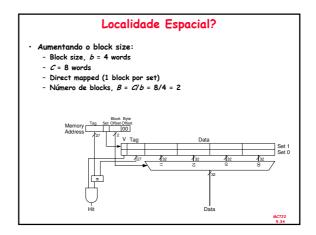

- Block size (b): tamanho do dado colocado na cache por vez

- · Number of blocks (B): número de blocks na cache

- Degree of associativity (N): número de blocks em um set (também, número de lugares aonde um endereço pode ser encontrado na cache)

MC722

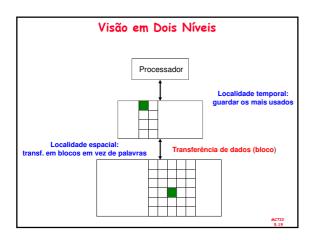

## Qual Dado Deve Ser Mantido na Cache?

- Idealmente, a cache deve ter o dado antecipadamente ao processador e mante-lo na cache

- · Porém, é impóssivel preve o futuro

- Assim, use o passado para preve o futuro use o principio da localidade (temporal e espacial):

- Localidadde Temporal: Se o processador acessa um dado que não está na cache, copia o dado do lower level para cache.

No próximo acesso ele estará na cache.

- Localidadde Espacial: copia também os vizinhos do dado para a cache. Block size = númeor de bytes copiedos para a cache de uma única vez.

MC722

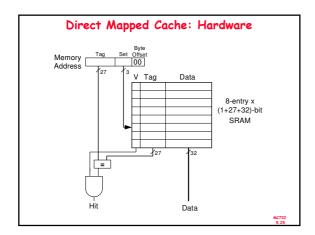

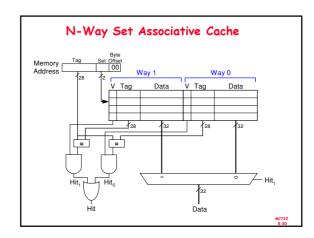

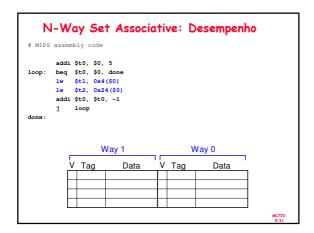

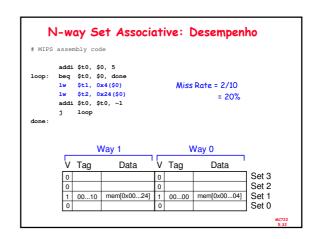

## Como Localizar um Dado na Cache?

- · A Cache é organizada em S conjuntos (sets)

- · Cada endereço de memória mapeia exatamente um set

- As Caches são categorizadas pelo número de blocos em um set:

- Direct mapped: 1 bloco por set

- N-way set associative: N blocos por set

- Fully associative: todos os blocos da cache estão em um mesmo set

- Exemplo: Examine cada uma das 3 organização para uma cache com:

- Capacidade (C = 8 words)

- Block size (b = 1 word)

- Assim, número de blocks (B = 8)

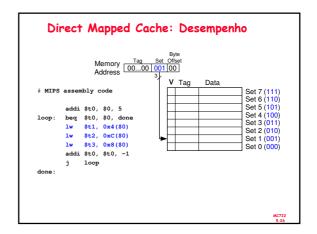

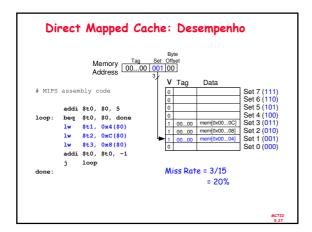

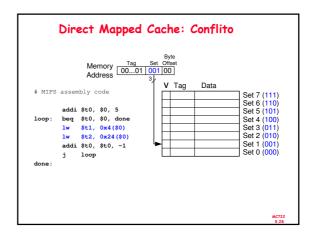

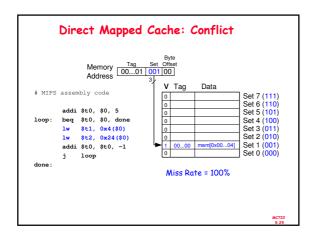

Direct Mapped: Cache Address 11...111**1110**0 11...111**110**00 11...111**10**100 11...111**100**00 11...111**011**00 11...111**010**00 11...111**001**00 11...11100000 00...001**001**00 mem[0x00...24] 00...001**000**00 00...000**111**00 00...000**110**00 Set Number 7 (111) 6 (110) 00...00010100 5 (101) 4 (100) 00...00010000 mem[0x00...10] mem[0x00...0C] 00...000**011**00 00...000**010**00 3 (011) 2 (010) 00...00000100 230 Word Main Memory 23 Word Cache

C722 5.23

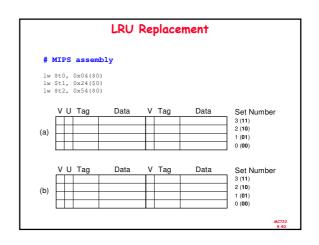

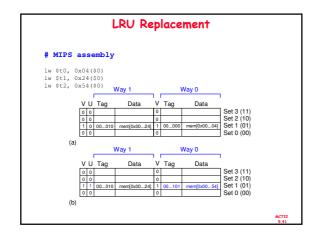

## Aonde colocar o Dado? • Least recently used (LRU): • O bloco usado a mais tempo é escolhido para ser retirado quando a cache esta "cheia".

## Cache

- · Políticas:

- mapeamento de endereços entre cache e memória

- substituição: qual bloco descartar da cache

- escrita: como fazer a consistência de dados entre cache e memória

## Etapas para uma Leitura na Cache (de Dados ou de Instruções)

- Enviar o endereço para a cache (vem do PC para leitura de instruções ou da ULA para leitura de dados)

- Se existir o sinal hit, significa que a palavra desejada está disponível na linha de dados. Se existir o sinal miss o endereço é enviado à memória principal, e quando o dado chega, é escrito na cache.

## Etapas para uma Escrita na Cache

- · Escrita (store)

- o dado tem que ser escrito na cache

valores diferentes entre cache e memória principal

- Inconsistência

- » escrever também na memória principal write-through.

- · Desempenho com write-through

- gcc tem 13% de instruções de store.

- Na DECStation 3100 o CPI para store é 1.2 e gasta 10

- nova CPI = 1.2+13% X 10 = 2.5

- reduz o desempenho por um fator maior que 2

- solução possível

## Etapas para uma Escrita na Cache

- Outro esquema de atualização da memória

- a memória só é atualizada quando o bloco da cache que sofreu modificação for substituído por outro

## Hits vs. Misses (política de atualização ou escrita)

- · Read hits

- É o desejado

- · Read misses

- stall a CPU, fetch block da memória, preencher a cache

- · Write hits:

- atualiza o dado na cache e na memória (write-through)

- atualiza o dado somente na cache (write-back depois)

- » também conhecida como copy-back

- » dirty bit

## Hits vs. Misses (política de atualização ou escrita)

- · Write misses:

- ler o block e coloca-lo na cache, então escrever o dado (Write-Allocate)

- dado escrito na cache pelo processador; não há leitura da memória principal; atualizar tag (no-Write Allocate)

- · Comparação

- desempenho: write-back

- confiabilidade: write-through

- proc. paralelo: write-through

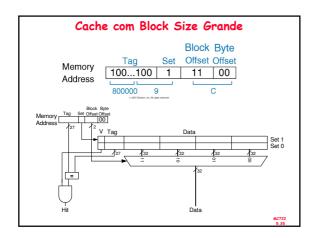

## Tamanho da Cache em Bits

- Número de bits necessários para uma cache é função do tamanho da cache e do tamanho do endereço (dados + tags)

- · Número de bits de uma cache

- Endereço de 32 bits, cache com mapeamento direto de 2º words com blocos de uma palavra (4 bytes)

- » 2 bits usados para offset do byte e n para o índice.

- » tag de 32 (n + 2).

- O número total de bits da cache

- » 2<sup>n</sup> X (32 + (32 n -2) + 1) = 2<sup>n</sup> X (63 n).

MC722

## Exemplo:

Quantos bits são necessários para uma cache com mapeamento direto com 64KB de capacidade para dados e bloco de uma palavra, assumindo endereço de 32 bits?

### Solução:

64KB → 16K palavras → 2<sup>14</sup> palavras → 2<sup>14</sup> blocos

Cada bloco tem 32 bits de dados mais o tag (32 - 14 - 2 = 16)

Total de bits da cache  $2^{14}$  X (32 + 16 + 1) = 784 Kbits = 98 KB

Para esta cache, temos um overhead de 1.5, devido aos tag e aos bits de validade.

MC722 5.51

## Tratamento de Cache Misses

- Quando a unidade de controle detecta um miss, ela busca o dado da memória. Se detecta um hit, continua o processamento como se nada tivesse acontecido.

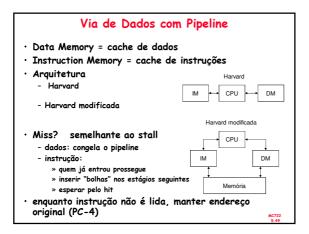

- · Mudança do datapath

- substituir as memórias por caches e alterar o controle para quando ocorrer miss.

- · Alteração do controle

- Atrasar (stall semelhante ao stall do pipeline, diferença que para todas as unidades do pipeline) da CPU, congelando o conteúdo de todos os registradores.

- Um controlador separado trata o miss, lendo o dado da memória.

HC722

## Etapas de um Cache Miss de uma Instrução

- Enviar o PC original ( PC corrente 4) para a memória

- $\cdot$  Fazer a leitura da memória e esperar o conteúdo

- Escrever na cache o dado vindo da memória, escrevendo os bits mais significativos do endereço (da ULA) no campo de tag e "setando" o bit de validade.

- · Reiniciar a execução da instrução.

Etapas de um Cache Miss de Dados

stall no processador até a memória enviar o dado (sinal de hit)

> MC722 5.54

MC722 5.53

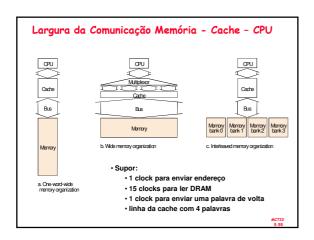

## Cálculo do Miss Penalty vs Largura Comunicação

- · Uma palavra de largura na memória:

- 1 + 4\*15 + 4\*1 = 65 ciclos (miss penalty) Bytes / ciclo para um miss: 4 \* 4 / 65 = 0,25 B/ck

- · Duas palavras de largura na memória:

- 1 + 2\*15 + 2\*1 = 33 ciclos

- Bytes / ciclo para um miss: 4 \* 4 / 33 = 0,48 B/ck

- · Quatro palavras de largura na memória:

- 1 + 1\*15 + 1\*1 = 17 ciclos

- Bytes / ciclo para um miss: 4 \* 4 / 17 = 0,94 B/ck

- Custo: multiplexador de 128 bits de largura e atraso

## Cálculo do Miss Penalty vs Largura Comunicação

- Tudo com uma palavra de largura mas 4 bancos de memória interleaved (intercalada)

- Tempo de leitura das memórias é paralelizado (ou

- » Mais comum: endereço bits mais significativos

- 1 + 1\*15 + 4\*1 = 20 ciclos

- Bytes / ciclo para um miss: 4 \* 4 / 20 = 0,8 B/ck

- funciona bem também em escrita (4 escritas simultâneas): » indicado para caches com write through

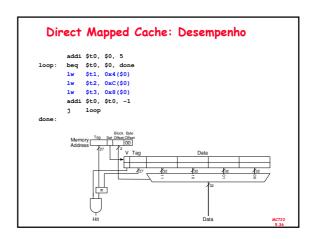

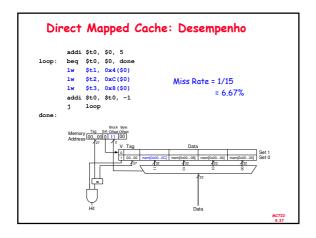

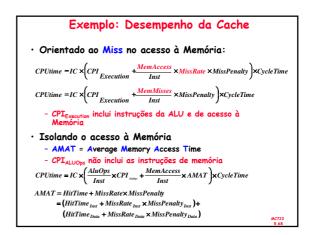

## Medida e Melhoria de Desempenho de Cache

· Modelo simplificado de Desempenho

execution time = (execution cycles + stall cycles) x cycle time stall cycles = (RD + WR) stalls

RD stall cycles = # de RDs  $\times$  RD miss ratio  $\times$  RD miss penalty

WR stall cycles = # de WRs  $\times$  WR miss ratio  $\times$  WR miss penalty

(mais complicado do que isto)

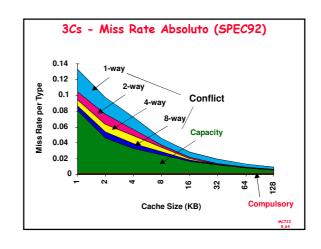

## Medida e Melhoria de Desempenho de Cache

- · Melhoria de Desempenho

- Redução da probabilidade de dois blocos diferentes serem alocados na mesma linha de cache.

- Redução do miss pela adição de mais um nível de cache na hierarquia (multilevel caching).

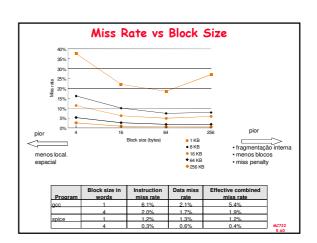

O que acontece se aumentarmos o tamanho do bloco?

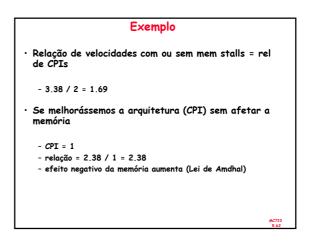

## Exemplo • gcc: instruction miss ratio = 2%; data cache miss rate = 4% • CPI = 2 (sem stalls de mem); miss penalty = 40 ciclos • Instructions misses cycles = I \* 2% \* 40 = 0.8 I • Sabendo que lw+sw = 36% • data miss cycles = I \* 36% \* 4% \* 40 = 0.58 I • No. de stalls de mem = 0.8 I + 0.58 I = 1.38 I • CPI total = 2 + 1.38 = 3.38

```

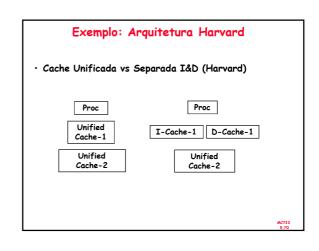

Exemplo: Arquitetura Harvard

• Suponha:

- 16KB I&D: Inst miss rate = 0.64%, Data miss rate = 6.47%

- 32KB unificada: miss rate = 1.99% (agregado)

- 33% das instruções são ops de dados (load ou store)

• Qual é melhor (ignore cache L2)?

- 33% ops de dados ⇒ 75% dos acessos são devidos a fetch das instruções (1.0/1.33)

- hit time = 1, miss time = 50

- Note que data hit tem 1 stall para a cache unificada (somente uma porta)

AMAT<sub>Harvard</sub> = 75%x(1+0.64%x50) + 25%x(1+6.47%x50) = 2.05

AMAT<sub>Unified</sub> = 75%x(1+1.99%x50) + 25%x(1+11.99%x50) = 2.24µcr22 5.71

```