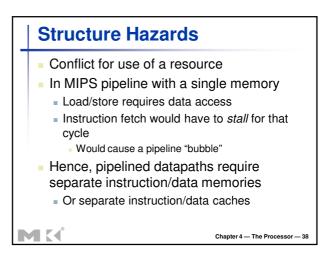

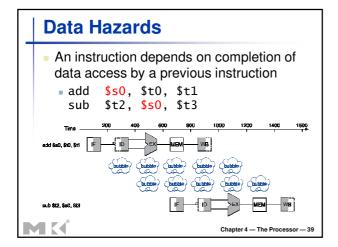

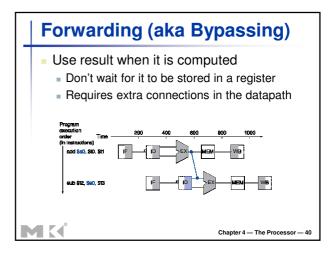

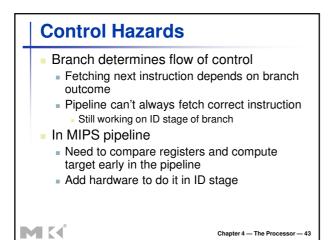

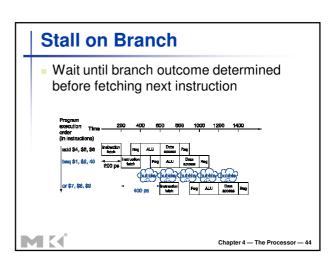

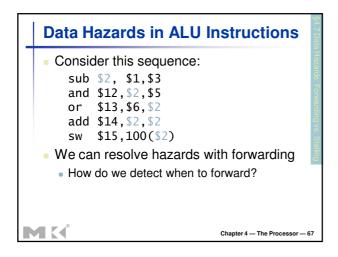

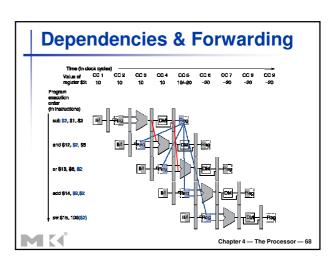

### Hazards Situations that prevent starting the next instruction in the next cycle Structure hazards A required resource is busy Data hazard Need to wait for previous instruction to complete its data read/write Control hazard Deciding on control action depends on previous instruction

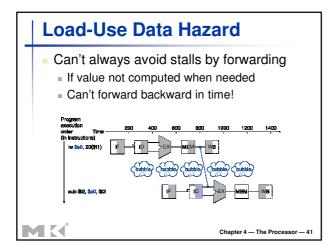

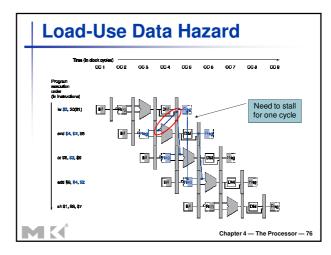

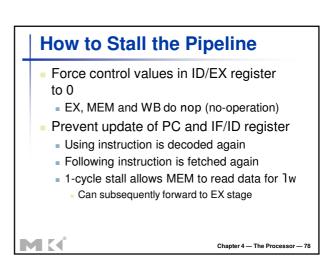

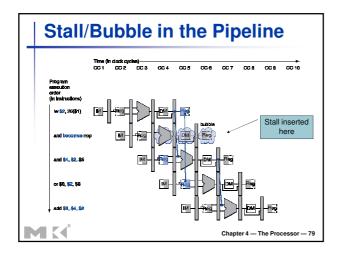

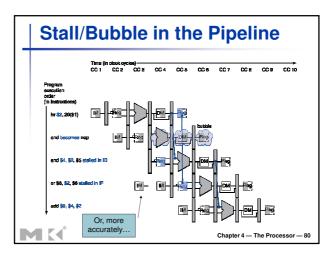

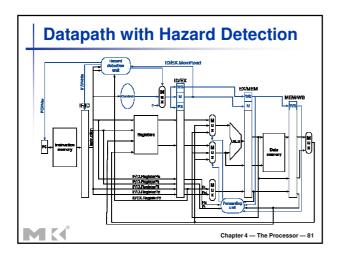

# Load-Use Hazard Detection Check when using instruction is decoded in ID stage ALU operand register numbers in ID stage are given by IF/ID.RegisterRs, IF/ID.RegisterRt Load-use hazard when ID/EX.MemRead and ((ID/EX.RegisterRt = IF/ID.RegisterRs) or (ID/EX.RegisterRt = IF/ID.RegisterRt)) If detected, stall and insert bubble

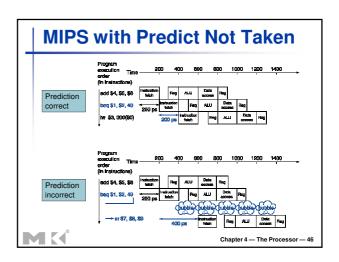

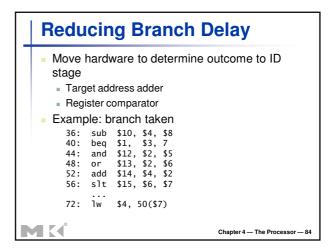

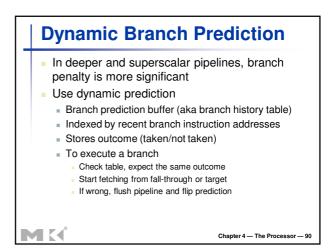

# Calculating the Branch Target Even with predictor, still need to calculate the target address 1-cycle penalty for a taken branch Branch target buffer Cache of target addresses Indexed by PC when instruction fetched If hit and instruction is branch predicted taken, can fetch target immediately

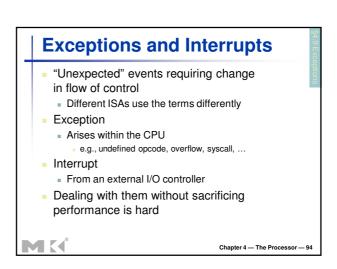

### Handler Actions Read cause, and transfer to relevant handler Determine action required If restartable Take corrective action use EPC to return to program Otherwise Terminate program Report error using EPC, cause, ...

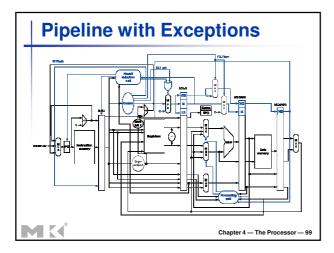

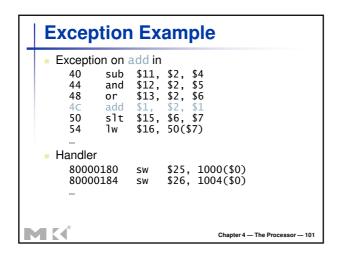

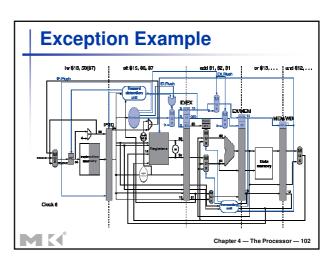

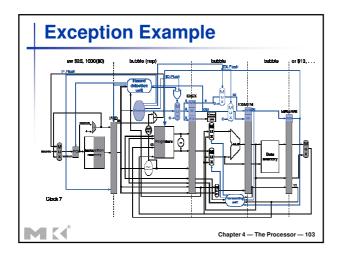

# Exceptions in a Pipeline - Another form of control hazard - Consider overflow on add in EX stage add \$1, \$2, \$1 - Prevent \$1 from being clobbered - Complete previous instructions - Flush add and subsequent instructions - Set Cause and EPC register values - Transfer control to handler - Similar to mispredicted branch - Use much of the same hardware

# Imprecise Exceptions Just stop pipeline and save state Including exception cause(s) Let the handler work out Which instruction(s) had exceptions Which to complete or flush May require "manual" completion Simplifies hardware, but more complex handler software Not feasible for complex multiple-issue out-of-order pipelines

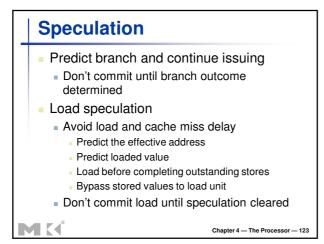

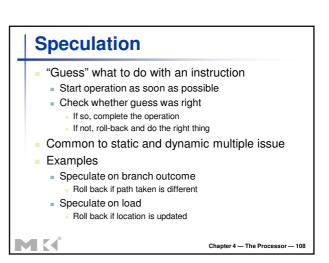

### **Compiler/Hardware Speculation**

- Compiler can reorder instructions

- e.g., move load before branch

- Can include "fix-up" instructions to recover from incorrect guess

- Hardware can look ahead for instructions to execute

- Buffer results until it determines they are actually needed

- Flush buffers on incorrect speculation

Chapter 4 — The Processor — 109

### **Speculation and Exceptions**

- What if exception occurs on a speculatively executed instruction?

- e.g., speculative load before null-pointer check

- Static speculation

- Can add ISA support for deferring exceptions

- Dynamic speculation

- Can buffer exceptions until instruction completion (which may not occur)

Chapter 4 — The Processor — 11

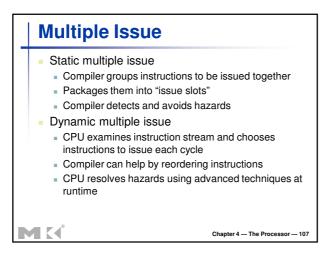

### **Static Multiple Issue**

- Compiler groups instructions into "issue packets"

- Group of instructions that can be issued on a single cycle

- Determined by pipeline resources required

- Think of an issue packet as a very long instruction

- Specifies multiple concurrent operations

- ⇒ Very Long Instruction Word (VLIW)

Chapter 4 — The Processor — 11

### **Scheduling Static Multiple Issue**

- Compiler must remove some/all hazards

- Reorder instructions into issue packets

- No dependencies with a packet

- Possibly some dependencies between packets

- Varies between ISAs; compiler must know!

- Pad with nop if necessary

Chapter 4 — The Processor — 112

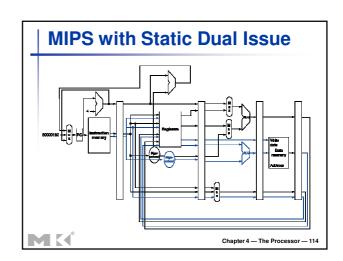

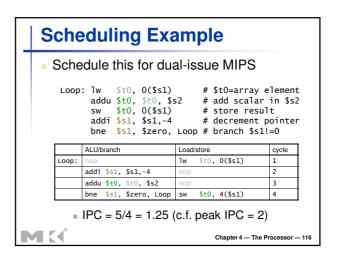

### **MIPS with Static Dual Issue**

- Two-issue packets

- One ALU/branch instruction

- One load/store instruction

- 64-bit aligned

- ALU/branch, then load/store

- Pad an unused instruction with nop

| Address | Instruction type | Pipeline Stages |    |    |     |     |     |    |

|---------|------------------|-----------------|----|----|-----|-----|-----|----|

| n       | ALU/branch       | IF              | ID | EX | MEM | WB  |     |    |

| n + 4   | Load/store       | IF              | ID | EX | MEM | WB  |     |    |

| n + 8   | ALU/branch       |                 | IF | ID | EX  | MEM | WB  |    |

| n + 12  | Load/store       |                 | IF | ID | EX  | MEM | WB  |    |

| n + 16  | ALU/branch       |                 |    | IF | ID  | EX  | MEM | WB |

| n + 20  | Load/store       |                 |    | IF | ID  | EX  | MEM | WB |

### **Hazards in the Dual-Issue MIPS**

- More instructions executing in parallel

- EX data hazard

- Forwarding avoided stalls with single-issue

- Now can't use ALU result in load/store in same packet

- add \$t0, \$s0, \$s1

load \$s2, 0(\$t0)

- Split into two packets, effectively a stall

- Load-use hazard

- Still one cycle use latency, but now two instructions

- More aggressive scheduling required

Chapter 4 — The Processor — 11

### **Loop Unrolling**

- Replicate loop body to expose more parallelism

- Reduces loop-control overhead

- Use different registers per replication

- Called "register renaming"

- Avoid loop-carried "anti-dependencies"

- Store followed by a load of the same register

- Aka "name dependence"

- Reuse of a register name

Chapter 4 — The Processor — 117

### **Loop Unrolling Example**

|       | ALU/branch             | Load/store        | cycle |

|-------|------------------------|-------------------|-------|

| Loop: | addi \$s1, \$s1,-16    | lw \$t0, 0(\$s1)  | 1     |

|       | nop                    | lw \$t1, 12(\$s1) | 2     |

|       | addu \$t0, \$t0, \$s2  | lw \$t2, 8(\$s1)  | 3     |

|       | addu \$t1, \$t1, \$s2  | lw \$t3, 4(\$s1)  | 4     |

|       | addu \$t2, \$t2, \$s2  | sw \$t0, 16(\$s1) | 5     |

|       | addu \$t3, \$t4, \$s2  | sw \$t1, 12(\$s1) | 6     |

|       | nop                    | sw \$t2, 8(\$s1)  | 7     |

|       | bne \$s1, \$zero, Loop | sw \$t3, 4(\$s1)  | 8     |

- IPC = 14/8 = 1.75

- Closer to 2, but at cost of registers and code size

Chapter 4 — The Processor — 118

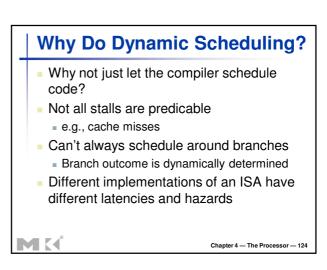

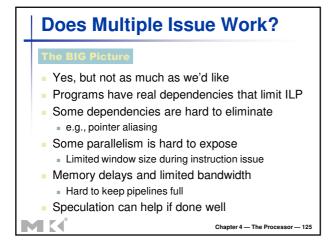

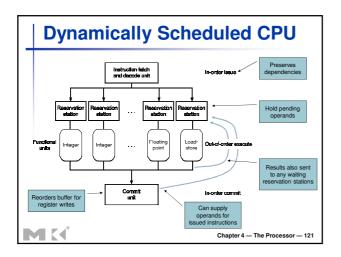

### **Dynamic Multiple Issue**

- "Superscalar" processors

- CPU decides whether to issue 0, 1, 2, ...

each cycle

- Avoiding structural and data hazards

- Avoids the need for compiler scheduling

- Though it may still help

- Code semantics ensured by the CPU

Chapter 4 — The Processor — 119

### **Dynamic Pipeline Scheduling**

- Allow the CPU to execute instructions out of order to avoid stalls

- But commit result to registers in order

- Example

```

lw $t0, 20($s2)

addu $t1, $t0, $t2

sub $s4, $s4, $t3

slti $t5, $s4, 20

```

Can start sub while addu is waiting for lw

### Register Renaming Reservation stations and reorder buffer effectively provide register renaming On instruction issue to reservation station If operand is available in register file or reorder buffer Copied to reservation station No longer required in the register; can be overwritten If operand is not yet available It will be provided to the reservation station by a function unit

Register update may not be required