## 4. AVR CPU Core

## 4.1 Introduction

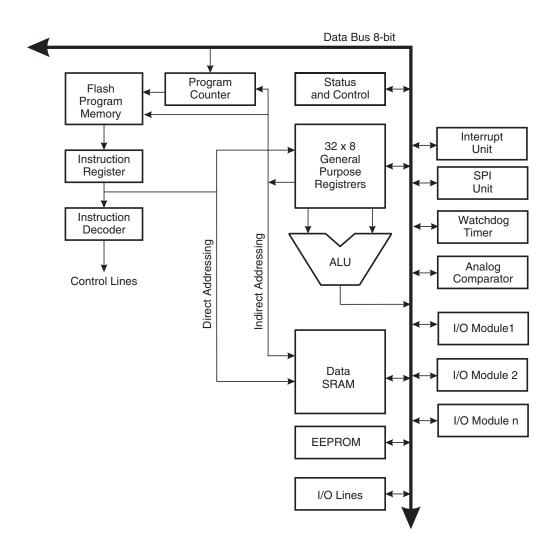

This section discusses the AVR core architecture in general. The main function of the CPU core is to ensure correct program execution. The CPU must therefore be able to access memories, perform calculations, control peripherals, and handle interrupts.

### 4.2 Architectural Overview

Figure 4-1. Block Diagram of the AVR Architecture

In order to maximize performance and parallelism, the AVR uses a Harvard architecture – with separate memories and buses for program and data. Instructions in the program memory are executed with a single level pipelining. While one instruction is being executed, the next instruction is pre-fetched from the program memory. This concept enables instructions to be executed in every clock cycle. The program memory is In-System Reprogrammable Flash memory.

### 4.4 Status Register

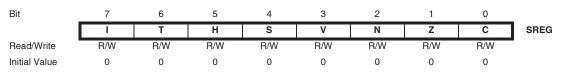

The Status Register contains information about the result of the most recently executed arithmetic instruction. This information can be used for altering program flow in order to perform conditional operations. Note that the Status Register is updated after all ALU operations, as specified in the Instruction Set Reference. This will in many cases remove the need for using the dedicated compare instructions, resulting in faster and more compact code.

The Status Register is not automatically stored when entering an interrupt routine and restored when returning from an interrupt. This must be handled by software.

The AVR Status Register - SREG - is defined as:

#### • Bit 7 – I: Global Interrupt Enable

The Global Interrupt Enable bit must be set for the interrupts to be enabled. The individual interrupt enable control is then performed in separate control registers. If the Global Interrupt Enable Register is cleared, none of the interrupts are enabled independent of the individual interrupt enable settings. The I-bit is cleared by hardware after an interrupt has occurred, and is set by the RETI instruction to enable subsequent interrupts. The I-bit can also be set and cleared by the application with the SEI and CLI instructions, as described in the instruction set reference.

#### • Bit 6 – T: Bit Copy Storage

The Bit Copy instructions BLD (Bit LoaD) and BST (Bit STore) use the T-bit as source or destination for the operated bit. A bit from a register in the Register File can be copied into T by the BST instruction, and a bit in T can be copied into a bit in a register in the Register File by the BLD instruction.

#### • Bit 5 – H: Half Carry Flag

The Half Carry Flag H indicates a Half Carry in some arithmetic operations. Half Carry Is useful in BCD arithmetic. See the "Instruction Set Description" for detailed information.

#### Bit 4 – S: Sign Bit, S = N ⊕ V

The S-bit is always an exclusive or between the Negative Flag N and the Two's Complement Overflow Flag V. See the "Instruction Set Description" for detailed information.

#### • Bit 3 – V: Two's Complement Overflow Flag

The Two's Complement Overflow Flag V supports two's complement arithmetics. See the "Instruction Set Description" for detailed information.

#### • Bit 2 – N: Negative Flag

The Negative Flag N indicates a negative result in an arithmetic or logic operation. See the "Instruction Set Description" for detailed information.

#### • Bit 1 – Z: Zero Flag

The Zero Flag Z indicates a zero result in an arithmetic or logic operation. See the "Instruction Set Description" for detailed information.

#### • Bit 0 – C: Carry Flag

The Carry Flag C indicates a carry in an arithmetic or logic operation. See the "Instruction Set Description" for detailed information.

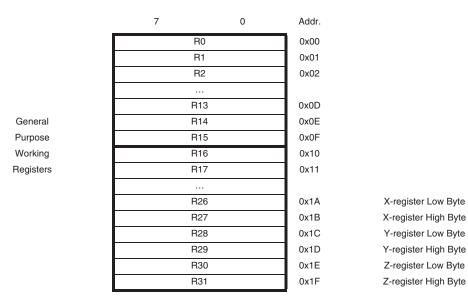

#### 4.5 General Purpose Register File

The Register File is optimized for the AVR Enhanced RISC instruction set. In order to achieve the required performance and flexibility, the following input/output schemes are supported by the Register File:

- One 8-bit output operand and one 8-bit result input

- Two 8-bit output operands and one 8-bit result input

- Two 8-bit output operands and one 16-bit result input

- One 16-bit output operand and one 16-bit result input

Figure 4-2 shows the structure of the 32 general purpose working registers in the CPU.

Figure 4-2. AVR CPU General Purpose Working Registers

Most of the instructions operating on the Register File have direct access to all registers, and most of them are single cycle instructions.

As shown in Figure 4-2, each register is also assigned a data memory address, mapping them directly into the first 32 locations of the user Data Space. Although not being physically implemented as SRAM locations, this memory organization provides great flexibility in access of the registers, as the X-, Y- and Z-pointer registers can be set to index any register in the file.

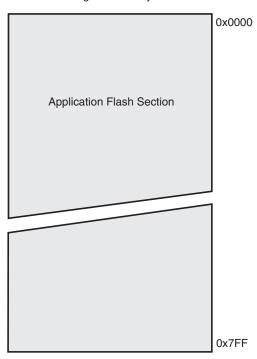

#### Figure 5-1. Program Memory Map, ATmega48

Program Memory

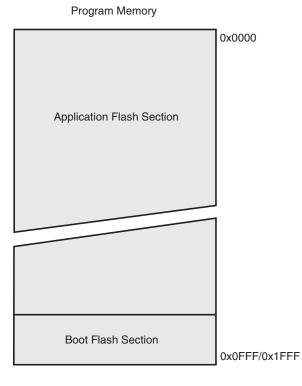

# Figure 5-2.Program Memory Map, ATmega88 and ATmega168

#### 5.2 SRAM Data Memory

Figure 5-3 shows how the ATmega48/88/168 SRAM Memory is organized.

The ATmega48/88/168 is a complex microcontroller with more peripheral units than can be supported within the 64 locations reserved in the Opcode for the IN and OUT instructions. For the Extended I/O space from 0x60 - 0xFF in SRAM, only the ST/STS/STD and LD/LDS/LDD instructions can be used.

The lower 768/1280/1280 data memory locations address both the Register File, the I/O memory, Extended I/O memory, and the internal data SRAM. The first 32 locations address the Register File, the next 64 location the standard I/O memory, then 160 locations of Extended I/O memory, and the next 512/1024/1024 locations address the internal data SRAM.

The five different addressing modes for the data memory cover: Direct, Indirect with Displacement, Indirect, Indirect with Pre-decrement, and Indirect with Post-increment. In the Register File, registers R26 to R31 feature the indirect addressing pointer registers.

The direct addressing reaches the entire data space.

The Indirect with Displacement mode reaches 63 address locations from the base address given by the Y- or Z-register.

When using register indirect addressing modes with automatic pre-decrement and post-increment, the address registers X, Y, and Z are decremented or incremented.

The 32 general purpose working registers, 64 I/O Registers, 160 Extended I/O Registers, and the 512/1024/1024 bytes of internal data SRAM in the ATmega48/88/168 are all accessible through all these addressing modes. The Register File is described in "General Purpose Register File" on page 10.

#### Figure 5-3. Data Memory Map

#### **Data Memory**

| 32 Registers<br>64 I/O Registers     | 0x0000 - 0x001F<br>0x0020 - 0x005F |

|--------------------------------------|------------------------------------|

| 160 Ext I/O Reg.                     | 0x0060 - 0x00FF                    |

|                                      | 0x0100                             |

| Internal SRAM<br>(512/1024/1024 x 8) |                                    |

|                                      | 0x02FF/0x04FF/0x04FF               |

#### 5.2.1 Data Memory Access Times

This section describes the general access timing concepts for internal memory access. The internal data SRAM access is performed in two  $clk_{CPU}$  cycles as described in Figure 5-4.

## 9.2 Interrupt Vectors in ATmega88

| Table 9-2. | Reset and Interrupt Vectors in ATmega8 | 88 |

|------------|----------------------------------------|----|

|            |                                        | 0  |

| Vector No. | Program<br>Address <sup>(2)</sup> | Source       | Interrupt Definition                                                    |

|------------|-----------------------------------|--------------|-------------------------------------------------------------------------|

| 1          | 0x000 <sup>(1)</sup>              | RESET        | External Pin, Power-on Reset, Brown-out Reset and Watchdog System Reset |

| 2          | 0x001                             | INTO         | External Interrupt Request 0                                            |

| 3          | 0x002                             | INT1         | External Interrupt Request 1                                            |

| 4          | 0x003                             | PCINT0       | Pin Change Interrupt Request 0                                          |

| 5          | 0x004                             | PCINT1       | Pin Change Interrupt Request 1                                          |

| 6          | 0x005                             | PCINT2       | Pin Change Interrupt Request 2                                          |

| 7          | 0x006                             | WDT          | Watchdog Time-out Interrupt                                             |

| 8          | 0x007                             | TIMER2 COMPA | Timer/Counter2 Compare Match A                                          |

| 9          | 0x008                             | TIMER2 COMPB | Timer/Counter2 Compare Match B                                          |

| 10         | 0x009                             | TIMER2 OVF   | Timer/Counter2 Overflow                                                 |

| 11         | 0x00A                             | TIMER1 CAPT  | Timer/Counter1 Capture Event                                            |

| 12         | 0x00B                             | TIMER1 COMPA | Timer/Counter1 Compare Match A                                          |

| 13         | 0x00C                             | TIMER1 COMPB | Timer/Coutner1 Compare Match B                                          |

| 14         | 0x00D                             | TIMER1 OVF   | Timer/Counter1 Overflow                                                 |

| 15         | 0x00E                             | TIMER0 COMPA | Timer/Counter0 Compare Match A                                          |

| 16         | 0x00F                             | TIMER0 COMPB | Timer/Counter0 Compare Match B                                          |

| 17         | 0x010                             | TIMER0 OVF   | Timer/Counter0 Overflow                                                 |

| 18         | 0x011                             | SPI, STC     | SPI Serial Transfer Complete                                            |

| 19         | 0x012                             | USART, RX    | USART Rx Complete                                                       |

| 20         | 0x013                             | USART, UDRE  | USART, Data Register Empty                                              |

| 21         | 0x014                             | USART, TX    | USART, Tx Complete                                                      |

| 22         | 0x015                             | ADC          | ADC Conversion Complete                                                 |

| 23         | 0x016                             | EE READY     | EEPROM Ready                                                            |

| 24         | 0x017                             | ANALOG COMP  | Analog Comparator                                                       |

| 25         | 0x018                             | TWI          | 2-wire Serial Interface                                                 |

| 26         | 0x019                             | SPM READY    | Store Program Memory Ready                                              |

Notes: 1. When the BOOTRST Fuse is programmed, the device will jump to the Boot Loader address at

reset, see "Boot Loader Support – Read-While-Write Self-Programming, ATmega88 and ATmega168" on page 264.

2. When the IVSEL bit in MCUCR is set, Interrupt Vectors will be moved to the start of the Boot Flash Section. The address of each Interrupt Vector will then be the address in this table added to the start address of the Boot Flash Section.

Table 9-3 shows reset and Interrupt Vectors placement for the various combinations of BOOTRST and IVSEL settings. If the program never enables an interrupt source, the Interrupt Vectors are not used, and regular program code can be placed at these locations. This is also the case if the Reset Vector is in the Application section while the Interrupt Vectors are in the Boot section or vice versa.

|         |       | 1                  | 5                               |

|---------|-------|--------------------|---------------------------------|

| BOOTRST | IVSEL | Reset Address      | Interrupt Vectors Start Address |

| 1       | 0     | 0x000              | 0x001                           |

| 1       | 1     | 0x000              | Boot Reset Address + 0x001      |

| 0       | 0     | Boot Reset Address | 0x001                           |

| 0       | 1     | Boot Reset Address | Boot Reset Address + 0x001      |

Table 9-3.

Reset and Interrupt Vectors Placement in ATmega88<sup>(1)</sup>

Note: 1. The Boot Reset Address is shown in Table 24-6 on page 276. For the BOOTRST Fuse "1" means unprogrammed while "0" means programmed.

The most typical and general program setup for the Reset and Interrupt Vector Addresses in ATmega88 is:

| Address Label | s Code                                                    |                | С   | omments                            |

|---------------|-----------------------------------------------------------|----------------|-----|------------------------------------|

| 0x000         | rjmp                                                      | RESET          | ;   | Reset Handler                      |

| 0x001         | rjmp                                                      | EXT_INT0       | ;   | IRQ0 Handler                       |

| 0x002         | rjmp                                                      | EXT_INT1       | ;   | IRQ1 Handler                       |

| 0x003         | rjmp                                                      | PCINT0         | ;   | PCINTO Handler                     |

| 0x004         | rjmp                                                      | PCINT1         | ;   | PCINT1 Handler                     |

| 0x005         | rjmp                                                      | PCINT2         | ;   | PCINT2 Handler                     |

| 0x006         | rjmp                                                      | WDT            | ;   | Watchdog Timer Handler             |

| 0x007         | rjmp                                                      | TIM2_COMPA     | ;   | Timer2 Compare A Handler           |

| 0X008         | rjmp                                                      | TIM2_COMPB     | ;   | Timer2 Compare B Handler           |

| 0x009         | rjmp                                                      | TIM2_OVF       | ;   | Timer2 Overflow Handler            |

| 0x00A         | rjmp                                                      | TIM1_CAPT      | ;   | Timer1 Capture Handler             |

| 0x00B         | rjmp                                                      | TIM1_COMPA     | ;   | Timer1 Compare A Handler           |

| 0x00C         | rjmp                                                      | TIM1_COMPB     | ;   | Timer1 Compare B Handler           |

| 0x00D         | rjmp                                                      | TIM1_OVF       | ;   | Timer1 Overflow Handler            |

| 0x00E         | rjmp                                                      | TIM0_COMPA     | ;   | Timer0 Compare A Handler           |

| 0x00F         | rjmp                                                      | TIM0_COMPB     | ;   | Timer0 Compare B Handler           |

| 0x010         | rjmp                                                      | TIM0_OVF       | ;   | Timer0 Overflow Handler            |

| 0x011         | rjmp                                                      | SPI_STC        | ;   | SPI Transfer Complete Handler      |

| 0x012         | rjmp                                                      | USART_RXC      | ;   | USART, RX Complete Handler         |

| 0x013         | rjmp                                                      | USART_UDRE     | ;   | USART, UDR Empty Handler           |

| 0x014         | rjmp                                                      | USART_TXC      | ;   | USART, TX Complete Handler         |

| 0x015         | rjmp                                                      | ADC            | ;   | ADC Conversion Complete Handler    |

| 0x016         | rjmp                                                      | EE_RDY         | ;   | EEPROM Ready Handler               |

| 0x017         | rjmp                                                      | ANA_COMP       | ;   | Analog Comparator Handler          |

| 0x018         | rjmp                                                      | TWI            | ;   | 2-wire Serial Interface Handler    |

| 0x019         | rjmp                                                      | SPM_RDY        | ;   | Store Program Memory Ready Handler |

| ;             |                                                           |                |     |                                    |

| 0x01ARESET:   | ldi                                                       | r16, high(RAME | IND | ); Main program start              |

| 0x01B         | out                                                       | SPH,r16        | ;   | Set Stack Pointer to top of RAM    |

| 0x01C         | ldi                                                       | r16, low(RAMEN | ID) |                                    |

| 0x01D         | out                                                       | SPL,r16        |     |                                    |

| 0x01E         | sei                                                       |                | ;   | Enable interrupts                  |

| 0x01F         | <inst< td=""><td>r&gt; xxx</td><td></td><td></td></inst<> | r> xxx         |     |                                    |

## 10.4 Register Description for I/O Ports

#### 10.4.1 The Port B Data Register – PORTB

| 10.4.1 | The Port B Da  | ta Register - | - PORTB   |        |        |        |        |        |        |        |       |

|--------|----------------|---------------|-----------|--------|--------|--------|--------|--------|--------|--------|-------|

|        |                | Bit           | 7         | 6      | 5      | 4      | 3      | 2      | 1      | 0      |       |

|        |                |               | PORTB7    | PORTB6 | PORTB5 | PORTB4 | PORTB3 | PORTB2 | PORTB1 | PORTB0 | PORTB |

|        |                | Read/Write    | R/W       | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |       |

|        |                | Initial Value | 0         | 0      | 0      | 0      | 0      | 0      | 0      | 0      |       |

|        |                |               |           |        |        |        |        |        |        |        |       |

| 10.4.2 | The Port B Da  | ta Direction  | Register  | – DDRB |        |        |        |        |        |        |       |

|        |                | Bit           | 7         | 6      | 5      | 4      | 3      | 2      | 1      | 0      |       |

|        |                |               | DDB7      | DDB6   | DDB5   | DDB4   | DDB3   | DDB2   | DDB1   | DDB0   | DDRB  |

|        |                | Read/Write    | R/W       | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |       |

|        |                | Initial Value | 0         | 0      | 0      | 0      | 0      | 0      | 0      | 0      |       |

|        |                |               |           |        |        |        |        |        |        |        |       |

| 10.4.3 | The Port B Inp | out Pins Add  | ress – Pl | NB     |        |        |        |        |        |        |       |

|        |                | Bit           | 7         | 6      | 5      | 4      | 3      | 2      | 1      | 0      |       |

|        |                |               | PINB7     | PINB6  | PINB5  | PINB4  | PINB3  | PINB2  | PINB1  | PINB0  | PINB  |

|        |                | Read/Write    | R         | R      | R      | R      | R      | R      | R      | R      |       |

|        |                | Initial Value | N/A       | N/A    | N/A    | N/A    | N/A    | N/A    | N/A    | N/A    |       |

|        |                |               |           |        |        |        |        |        |        |        |       |

| 10.4.4 | The Port C Da  | ta Register - | - PORTC   |        |        |        |        |        |        |        |       |

|        |                | Bit           | 7         | 6      | 5      | 4      | 3      | 2      | 1      | 0      |       |

|        |                |               | -         | PORTC6 | PORTC5 | PORTC4 | PORTC3 | PORTC2 | PORTC1 | PORTC0 | PORTC |

|        |                | Read/Write    | R         | R/W    |       |

|        |                | Initial Value | 0         | 0      | 0      | 0      | 0      | 0      | 0      | 0      |       |

|        |                |               |           |        |        |        |        |        |        |        |       |

| 10.4.5 | The Port C Da  | ta Direction  | Register  | – DDRC |        |        |        |        |        |        |       |

|        |                | Bit           | 7         | 6      | 5      | 4      | 3      | 2      | 1      | 0      |       |

|        |                |               | -         | DDC6   | DDC5   | DDC4   | DDC3   | DDC2   | DDC1   | DDC0   | DDRC  |

|        |                | Read/Write    | R         | R/W    |       |

|        |                | Initial Value | 0         | 0      | 0      | 0      | 0      | 0      | 0      | 0      |       |

|        |                |               |           |        |        |        |        |        |        |        |       |

| 10.4.6 | The Port C Inp | out Pins Add  | ress – Pl | NC     |        |        |        |        |        |        |       |

|        |                | Bit           | 7         | 6      | 5      | 4      | 3      | 2      | 1      | 0      |       |

|        |                |               | -         | PINC6  | PINC5  | PINC4  | PINC3  | PINC2  | PINC1  | PINC0  | PINC  |

|        |                | Read/Write    | R         | R      | R      | R      | R      | R      | R      | R      |       |

|        |                | Initial Value | 0         | N/A    |       |

| 10.4.7 |                | to Deviator   |           |        |        |        |        |        |        |        |       |

| 10.4.7 | The Port D Da  | ta Register - | - PORID   |        |        |        |        |        |        |        |       |

|        |                | Bit           | 7         | 6      | 5      | 4      | 3      | 2      | 1      | 0      |       |

|        |                |               | PORTD7    | PORTD6 | PORTD5 | PORTD4 | PORTD3 | PORTD2 | PORTD1 | PORTD0 | PORTD |

|        |                | Read/Write    | R/W       | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |       |

|        |                | Initial Value | 0         | 0      | 0      | 0      | 0      | 0      | 0      | 0      |       |

| 10 4 9 | The Deut D De  | to Direction  | Dogister  | 0000   |        |        |        |        |        |        |       |

| 10.4.8 | The Port D Da  |               | -         |        |        |        |        |        |        |        |       |

|        |                | Bit           | 7         | 6      | 5      | 4      | 3      | 2      | 1      | 0      |       |

|        |                |               | DDD7      | DDD6   | DDD5   | DDD4   | DDD3   | DDD2   | DDD1   | DDD0   | DDRD  |

|        |                | Read/Write    | R/W       | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |       |

Initial Value

# 336 ATmega48/88/168

| Address                                                  | Name                                     | Bit 7                                  | Bit 6                 | Bit 5                            | Bit 4                  | Bit 3                  | Bit 2                | Bit 1                 | Bit 0                 | Page           |  |  |  |  |

|----------------------------------------------------------|------------------------------------------|----------------------------------------|-----------------------|----------------------------------|------------------------|------------------------|----------------------|-----------------------|-----------------------|----------------|--|--|--|--|

| (0x7D)                                                   | Reserved                                 | -                                      | -                     | -                                | -                      | -                      | -                    | -                     | -                     |                |  |  |  |  |

| (0x7C)                                                   | ADMUX                                    | REFS1                                  | REFS0                 | ADLAR                            | -                      | MUX3                   | MUX2                 | MUX1                  | MUX0                  | 250            |  |  |  |  |

| (0x7B)                                                   | ADCSRB                                   | -                                      | ACME                  | -                                | -                      | -                      | ADTS2                | ADTS1                 | ADTS0                 | 253            |  |  |  |  |

| (0x7A)                                                   | ADCSRA                                   | ADEN                                   | ADSC                  | ADATE                            | ADIF                   | ADIE                   | ADPS2                | ADPS1                 | ADPS0                 | 251            |  |  |  |  |

| (0x79)                                                   | ADCH                                     |                                        |                       |                                  | ADC Data Reg           | gister High byte       |                      |                       |                       | 253            |  |  |  |  |

| (0x78)                                                   | ADCL                                     |                                        |                       |                                  | ADC Data Reg           | gister Low byte        |                      |                       |                       | 253            |  |  |  |  |

| (0x77)                                                   | Reserved                                 | -                                      | -                     | -                                | -                      | -                      | -                    | -                     | -                     |                |  |  |  |  |

| (0x76)                                                   | Reserved                                 | -                                      | -                     | -                                | -                      | -                      | -                    | -                     | -                     |                |  |  |  |  |

| (0x75)                                                   | Reserved                                 | -                                      | -                     | -                                | -                      | -                      | -                    | -                     | -                     |                |  |  |  |  |

| (0x74)                                                   | Reserved                                 | -                                      | -                     | -                                | -                      | -                      | -                    | -                     | -                     |                |  |  |  |  |

| (0x73)                                                   | Reserved                                 | -                                      | -                     | -                                | -                      | -                      | -                    | -                     | -                     |                |  |  |  |  |

| (0x72)                                                   | Reserved                                 | -                                      | -                     | -                                | -                      | -                      | -                    | -                     | -                     |                |  |  |  |  |

| (0x71)                                                   | Reserved                                 | -                                      | -                     | -                                | -                      | -                      | -                    | -                     | -                     |                |  |  |  |  |

| (0x70)                                                   | TIMSK2                                   | -                                      | -                     | -                                | -                      | -                      | OCIE2B               | OCIE2A                | TOIE2                 | 154            |  |  |  |  |

| (0x6F)                                                   | TIMSK1                                   | -                                      | -                     | ICIE1                            | -                      | -                      | OCIE1B               | OCIE1A                | TOIE1                 | 133            |  |  |  |  |

| (0x6E)                                                   | TIMSK0                                   | -                                      | -                     | -                                | -                      | -                      | OCIE0B               | OCIE0A                | TOIE0                 | 104            |  |  |  |  |

| (0x6D)                                                   | PCMSK2                                   | PCINT23                                | PCINT22               | PCINT21                          | PCINT20                | PCINT19                | PCINT18              | PCINT17               | PCINT16               | 87             |  |  |  |  |

| (0x6C)                                                   | PCMSK1                                   | -                                      | PCINT14               | PCINT13                          | PCINT12                | PCINT11                | PCINT10              | PCINT9                | PCINT8                | 87             |  |  |  |  |

| (0x6B)                                                   | PCMSK0                                   | PCINT7                                 | PCINT6                | PCINT5                           | PCINT4                 | PCINT3                 | PCINT2               | PCINT1                | PCINT0                | 87             |  |  |  |  |

| (0x6A)                                                   | Reserved                                 | -                                      | -                     | -                                | -                      | -                      | -                    | -                     | -                     |                |  |  |  |  |

| (0x69)                                                   | EICRA                                    | -                                      | -                     | -                                | -                      | ISC11                  | ISC10                | ISC01                 | ISC00                 | 84             |  |  |  |  |

| (0x68)                                                   | PCICR                                    | -                                      | -                     | -                                | -                      | -                      | PCIE2                | PCIE1                 | PCIE0                 |                |  |  |  |  |

| (0x67)                                                   | Reserved                                 | -                                      | -                     | -                                | -                      | -                      | -                    | -                     | -                     |                |  |  |  |  |

| (0x66)                                                   | OSCCAL                                   |                                        |                       |                                  | Oscillator Calib       | pration Register       |                      |                       |                       | 32             |  |  |  |  |

| (0x65)                                                   | Reserved                                 | -                                      | -                     | -                                | -                      | -                      | -                    | -                     | -                     |                |  |  |  |  |

| (0x64)                                                   | PRR                                      | PRTWI                                  | PRTIM2                | PRTIM0                           | _                      | PRTIM1                 | PRSPI                | PRUSART0              | PRADC                 | 40             |  |  |  |  |

| (0x63)                                                   | Reserved                                 | -                                      | -                     | -                                | _                      | _                      | -                    | -                     | -                     |                |  |  |  |  |

| (0x62)                                                   | Reserved                                 | -                                      | -                     | -                                | -                      | -                      | -                    | -                     | -                     |                |  |  |  |  |

| (0x61)                                                   | CLKPR                                    | CLKPCE                                 | -                     | -                                | -                      | CLKPS3                 | CLKPS2               | CLKPS1                | CLKPS0                | 35             |  |  |  |  |

| (0x60)                                                   | WDTCSR                                   | WDIF                                   | WDIE                  | WDP3                             | WDCE                   | WDE                    | WDP2                 | WDP1                  | WDP0                  | 52             |  |  |  |  |

| 0x3F (0x5F)                                              | SREG                                     | 1                                      | Т                     | н                                | S                      | V                      | N                    | Z                     | С                     | 9              |  |  |  |  |

| 0x3E (0x5E)                                              | SPH                                      | -                                      | -                     | -                                | -                      | -                      | (SP10) <sup>5.</sup> | SP9                   | SP8                   | 11             |  |  |  |  |

| 0x3D (0x5D)                                              | SPL                                      | SP7                                    | SP6                   | SP5                              | SP4                    | SP3                    | SP2                  | SP1                   | SP0                   | 11             |  |  |  |  |

| 0x3C (0x5C)                                              | Reserved                                 | -                                      | -                     | -                                | -                      | -                      | -                    | -                     | -                     |                |  |  |  |  |

| 0x3B (0x5B)                                              | Reserved                                 | -                                      | -                     | -                                | -                      | -                      | -                    | -                     | -                     |                |  |  |  |  |

| 0x3A (0x5A)                                              | Reserved                                 | -                                      | -                     | -                                | -                      | -                      | -                    | -                     | -                     |                |  |  |  |  |

| 0x39 (0x59)                                              | Reserved                                 | -                                      | -                     | -                                | -                      | -                      | -                    | -                     | -                     |                |  |  |  |  |

| 0x38 (0x58)                                              | Reserved                                 | -                                      | -                     | -                                | -                      | -                      | -                    | -                     | -                     |                |  |  |  |  |

| 0x37 (0x57)                                              | SPMCSR                                   | SPMIE                                  | (RWWSB) <sup>5.</sup> | -                                | (RWWSRE) <sup>5.</sup> | BLBSET                 | PGWRT                | PGERS                 | SELFPRGEN             | 269            |  |  |  |  |

| 0x36 (0x56)                                              | Reserved                                 | -                                      | -                     | -                                | -                      | -                      | -                    | -                     | -                     |                |  |  |  |  |

| 0x35 (0x55)                                              | MCUCR                                    | -                                      | -                     | -                                | PUD                    | -                      | -                    | IVSEL                 | IVCE                  |                |  |  |  |  |

| 0x34 (0x54)                                              | MCUSR                                    | -                                      | -                     | -                                | -                      | WDRF                   | BORF                 | EXTRF                 | PORF                  |                |  |  |  |  |

| 0x33 (0x53)                                              | SMCR                                     | -                                      | -                     | -                                | -                      | SM2                    | SM1                  | SM0                   | SE                    | 37             |  |  |  |  |

| 0x32 (0x52)                                              | Reserved                                 | -                                      | -                     | -                                | -                      | -                      | -                    | -                     | -                     |                |  |  |  |  |

| 0x31 (0x51)                                              | Reserved                                 | -                                      | -                     | -                                | -                      | -                      | -                    | -                     | -                     |                |  |  |  |  |

| 0x30 (0x50)                                              | ACSR                                     | ACD                                    | ACBG                  | ACO                              | ACI                    | ACIE                   | ACIC                 | ACIS1                 | ACIS0                 | 236            |  |  |  |  |

| 0x2F (0x4F)                                              | Reserved                                 | -                                      | -                     | -                                | -                      | -                      | -                    | -                     | -                     |                |  |  |  |  |

| 0x2E (0x4E)                                              | SPDR                                     |                                        |                       |                                  |                        | a Register             |                      |                       |                       | 166            |  |  |  |  |

| 0x2D (0x4D)                                              | SPSR                                     | SPIF                                   | WCOL                  | -                                | -                      | -                      | -                    | -                     | SPI2X                 | 166            |  |  |  |  |

| 0x2C (0x4C)                                              | SPCR                                     | SPIE                                   | SPE                   | DORD                             | MSTR                   | CPOL                   | CPHA                 | SPR1                  | SPR0                  | 164            |  |  |  |  |

| 0x2B (0x4B)                                              | GPIOR2                                   |                                        |                       |                                  |                        | se I/O Register 2      |                      |                       |                       | 24             |  |  |  |  |

| 0x2A (0x4A)                                              | GPIOR1                                   |                                        |                       |                                  |                        | se I/O Register 1      |                      |                       |                       | 24             |  |  |  |  |

| 0x29 (0x49)                                              | Reserved                                 | -                                      | -                     | -                                | -                      | -                      | -                    | -                     | -                     |                |  |  |  |  |

| 0x28 (0x48)                                              | OCR0B                                    |                                        |                       |                                  | mer/Counter0 Outp      |                        |                      |                       |                       |                |  |  |  |  |

| 0x27 (0x47)                                              | OCR0A                                    | ļ                                      |                       | Tir                              | mer/Counter0 Outp      | , ,                    | ster A               |                       |                       |                |  |  |  |  |

| 0x26 (0x46)                                              | TCNT0                                    |                                        |                       |                                  |                        | nter0 (8-bit)          |                      |                       |                       |                |  |  |  |  |

| 0x25 (0x45)                                              | TCCR0B                                   | FOC0A                                  | FOC0B                 | -                                | -                      | WGM02                  | CS02                 | CS01                  | CS00                  |                |  |  |  |  |

| 0x24 (0x44)                                              | TCCR0A                                   | COM0A1                                 | COM0A0                | COM0B1                           | COM0B0                 | -                      | -                    | WGM01                 | WGM00                 |                |  |  |  |  |

| 0x23 (0x43)                                              | GTCCR                                    | TSM                                    | -                     | -                                | -                      | _                      | -                    | PSRASY                | PSRSYNC               | 137/158<br>19  |  |  |  |  |

|                                                          | 1                                        | (EEPROM Address Register High Byte) 5. |                       |                                  |                        |                        |                      |                       |                       |                |  |  |  |  |

| 0x22 (0x42)                                              | EEARH                                    |                                        |                       | EEPROM Address Register Low Byte |                        |                        |                      |                       |                       |                |  |  |  |  |

| 0x21 (0x41)                                              | 1                                        |                                        |                       | ```                              | EEPROM Address         | Register Low By        | rte                  |                       |                       | 19             |  |  |  |  |

| 0x21 (0x41)<br>0x20 (0x40)                               | EEARH<br>EEARL<br>EEDR                   |                                        |                       |                                  | EEPROM D               | ata Register           |                      |                       |                       | 19             |  |  |  |  |

| 0x21 (0x41)<br>0x20 (0x40)<br>0x1F (0x3F)                | EEARH<br>EEARL<br>EEDR<br>EECR           |                                        | -                     | EEPM1                            | EEPROM D<br>EEPM0      | eata Register<br>EERIE | EEMPE                | EEPE                  | EERE                  | 19<br>19       |  |  |  |  |

| 0x21 (0x41)<br>0x20 (0x40)<br>0x1F (0x3F)<br>0x1E (0x3E) | EEARH<br>EEARL<br>EEDR<br>EECR<br>GPIOR0 | _                                      | _                     |                                  | EEPROM D<br>EEPM0      | ata Register           |                      |                       |                       | 19<br>19<br>24 |  |  |  |  |

| 0x21 (0x41)<br>0x20 (0x40)<br>0x1F (0x3F)                | EEARH<br>EEARL<br>EEDR<br>EECR           |                                        |                       |                                  | EEPROM D<br>EEPM0      | eata Register<br>EERIE |                      | EEPE<br>INT1<br>INTF1 | EERE<br>INT0<br>INTF0 | 19<br>19       |  |  |  |  |

# ATmega48/88/168

| Address     | Name     | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Page |

|-------------|----------|--------|--------|--------|--------|--------|--------|--------|--------|------|

| 0x1B (0x3B) | PCIFR    | -      | -      | -      | -      | -      | PCIF2  | PCIF1  | PCIF0  |      |

| 0x1A (0x3A) | Reserved | -      | -      | -      | -      | -      | -      | -      | -      |      |

| 0x19 (0x39) | Reserved | -      | -      | -      | -      | -      | -      | -      | -      |      |

| 0x18 (0x38) | Reserved | -      | -      | -      | -      | -      | -      | -      | -      |      |

| 0x17 (0x37) | TIFR2    | -      | -      | -      | -      | -      | OCF2B  | OCF2A  | TOV2   | 154  |

| 0x16 (0x36) | TIFR1    | -      | -      | ICF1   | -      | -      | OCF1B  | OCF1A  | TOV1   | 134  |

| 0x15 (0x35) | TIFR0    | -      | -      | -      | -      | -      | OCF0B  | OCF0A  | TOV0   |      |

| 0x14 (0x34) | Reserved | -      | -      | -      | -      | -      | -      | -      | -      |      |

| 0x13 (0x33) | Reserved | -      | -      | -      | -      | -      | -      | -      | -      |      |

| 0x12 (0x32) | Reserved | -      | -      | -      | -      | -      | -      | -      | -      |      |

| 0x11 (0x31) | Reserved | -      | -      | -      | -      | -      | -      | -      | -      |      |

| 0x10 (0x30) | Reserved | -      | -      | -      | -      | -      | -      | -      | -      |      |

| 0x0F (0x2F) | Reserved | -      | -      | -      | -      | -      | -      | -      | -      |      |

| 0x0E (0x2E) | Reserved | -      | -      | -      | -      | -      | -      | -      | -      |      |

| 0x0D (0x2D) | Reserved | -      | -      | -      | -      | -      | -      | -      | -      |      |

| 0x0C (0x2C) | Reserved | -      | -      | -      | -      | -      | -      | -      | -      |      |

| 0x0B (0x2B) | PORTD    | PORTD7 | PORTD6 | PORTD5 | PORTD4 | PORTD3 | PORTD2 | PORTD1 | PORTD0 | 81   |

| 0x0A (0x2A) | DDRD     | DDD7   | DDD6   | DDD5   | DDD4   | DDD3   | DDD2   | DDD1   | DDD0   | 81   |

| 0x09 (0x29) | PIND     | PIND7  | PIND6  | PIND5  | PIND4  | PIND3  | PIND2  | PIND1  | PIND0  | 82   |

| 0x08 (0x28) | PORTC    | -      | PORTC6 | PORTC5 | PORTC4 | PORTC3 | PORTC2 | PORTC1 | PORTC0 | 81   |

| 0x07 (0x27) | DDRC     | -      | DDC6   | DDC5   | DDC4   | DDC3   | DDC2   | DDC1   | DDC0   | 81   |

| 0x06 (0x26) | PINC     | -      | PINC6  | PINC5  | PINC4  | PINC3  | PINC2  | PINC1  | PINC0  | 81   |

| 0x05 (0x25) | PORTB    | PORTB7 | PORTB6 | PORTB5 | PORTB4 | PORTB3 | PORTB2 | PORTB1 | PORTB0 | 81   |

| 0x04 (0x24) | DDRB     | DDB7   | DDB6   | DDB5   | DDB4   | DDB3   | DDB2   | DDB1   | DDB0   | 81   |

| 0x03 (0x23) | PINB     | PINB7  | PINB6  | PINB5  | PINB4  | PINB3  | PINB2  | PINB1  | PINB0  | 81   |

| 0x02 (0x22) | Reserved | -      | -      | -      | -      | -      | -      | -      | -      |      |

| 0x01 (0x21) | Reserved | -      | -      | -      | -      | -      | -      | -      | -      |      |

| 0x0 (0x20)  | Reserved | -      | -      | -      | -      | -      | -      | -      | -      |      |

Note: 1. For compatibility with future devices, reserved bits should be written to zero if accessed. Reserved I/O memory addresses should never be written.

2. I/O Registers within the address range 0x00 - 0x1F are directly bit-accessible using the SBI and CBI instructions. In these registers, the value of single bits can be checked by using the SBIS and SBIC instructions.

- Some of the Status Flags are cleared by writing a logical one to them. Note that, unlike most other AVRs, the CBI and SBI instructions will only operate on the specified bit, and can therefore be used on registers containing such Status Flags. The CBI and SBI instructions work with registers 0x00 to 0x1F only.

- 4. When using the I/O specific commands IN and OUT, the I/O addresses 0x00 0x3F must be used. When addressing I/O Registers as data space using LD and ST instructions, 0x20 must be added to these addresses. The ATmega48/88/168 is a complex microcontroller with more peripheral units than can be supported within the 64 location reserved in Opcode for the IN and OUT instructions. For the Extended I/O space from 0x60 0xFF in SRAM, only the ST/STS/STD and LD/LDS/LDD instructions can be used.

- 5. Only valid for ATmega88/168

- Low Power Consumption

- Active Mode:

- 1 MHz, 1.8V: 240µA

- 32 kHz, 1.8V: 15µA (including Oscillator)

- Power-down Mode:

- 0.1µA at 1.8V

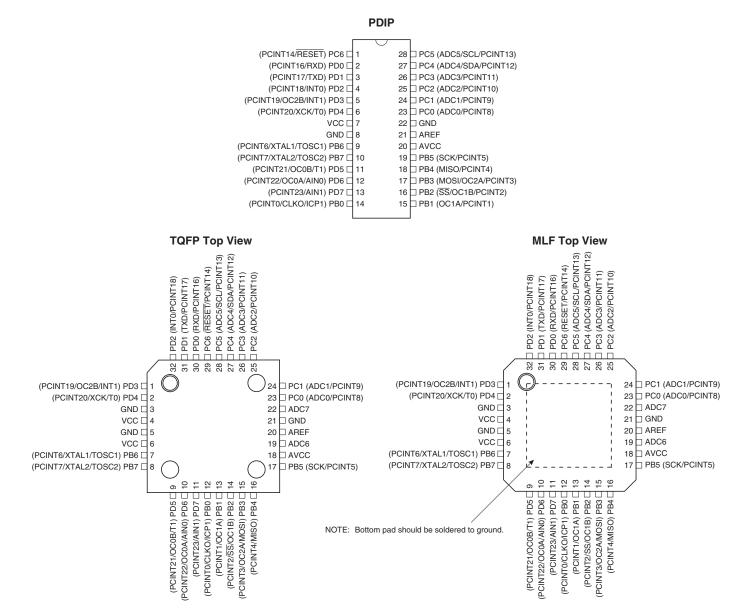

## 1. Pin Configurations

Figure 1-1. Pinout ATmega48/88/168